## InAs/InP コアシェルナノワイヤ縦型サラウンディング ゲートトランジスタにおける変調ドープ構造の検討

Modulation doping effect on vertical surrounding-gate transistors using InAs/InP core-shell nanowires

北海道大学情報科学研究科および量子集積センター

○蒲生 浩憲、本久 順一、冨岡 克広

Graduate School of IST and RCIQE, Hokkaido Univ. °Hironori Gamo, Junichi Motohisa, Katsuhiro Tomioka

E-mail:gamou@rciqe.hokudai.ac.jp

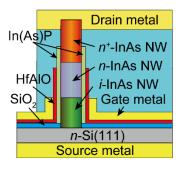

[はじめに] 電界効果トランジスタ(Fieldeffect transistors: FETs)の微細化によって、集積 回路は高性能化・低消費電力化を実現してきた が、微細化限界に近づき、低消費電力化が難し くなっている。そのため、III-V 族化合物半導 体ナノワイヤ(NW)が、高移動度で縦型チャネ ル構造になることから次世代 FET チャネル材 料として注目されている。さらに、ナノワイヤ コアシェル(CS)構造は、チャネル全面に変調ド ープ構造を形成できる利点がある[1]。我々は、 これまでに、Si 上に垂直配向した InAs NW を 用いたサラウンディングゲートトランジスタ (SGT)を作製してきたが、オン電流増大が課題 であった。本報告では、InAs/InP CS 構造の二 次元電子ガス(2DEG)形成について検討する。 [実験結果] 基板は熱酸化膜(20 nm)を形成した n型Si(111)を用い、有機金属気相(MOVPE)選択 成長法で、InAs NW を成長した。InAs NW は、 下部から Zn パルスドープ層、Si ドープ層、Sn パルスドープ層で構成されている。また、NW チャネル形成後、膜厚 7 nm の InAsP シェル層 を NW の側壁に形成した。次に、原子層堆積法 により HfAlO 膜を 10 nm 堆積し、スパッタリ ング法によりゲート電極(W)を成膜した。ベン ゾシクロブテン(BCB)により NW を包埋し、反 応性イオンエッチングで NW 上部のゲート電 極、HfAlO1 膜をエッチングすることで、サラウンディングゲート構造を作製した。最後に、BCB でゲート・ドレイン間分離層を形成し、NW 上部、基板裏面にそれぞれドレイン電極(Ti/Pd/Au)、ソース電極(Ni/Au)を蒸着し、図 1の縦型 SGT を作製した[2]。

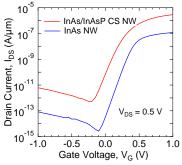

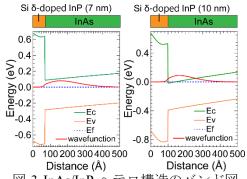

[結果] 図 2 に InAs NW SGT と InAs/InAsP CS NW SGT の伝達特性を示す。InAs/InAsP CS NW の特性は、SS = 88 mV/桁、 $I_{ON}/I_{OFF} = \sim 10^5$  であ った。InAs NW と比較すると、オン電流が1桁 増大するが、2DEG 特有の高いオン電流は得ら れなかった。これは、ソースキャリア密度が低 いことと、変調ドープ構造の設計に問題がある ためである。InAs/InP ヘテロ界面について、1 次元 Poisson-Schrödinger 方程式によるバンド 構造と波動関数の計算結果を図3に示す。図3 から、シェル膜厚 7 nm の場合、InAs チャネル 内ではキャリアの閉じ込めは生じず、シェル膜 厚を 10 nm 以上にすると、チャネル界面近傍に 2DEG が形成され始めることが分かった。当日 は、この設計指針をもとに、InAs/InP CS NW SGT のオン電流増大化について検討する。

## [参考文献]

[1] S. Morkötter *et al.*, Nano Lett. **15** (2015) 3295-3302

[2] H. Gamo, K. Tomioka. JCG 500 (2018) 58

図 1 InAs/In(As)P CS NW 縦型 SGT の模式図。

図 2 InAs/InAsP CS NW とInAs NW SGT の伝達特性。

図 3 InAs/InP ヘテロ構造のバンド図と基底状態波動関数の計算。