## InP ナノワイヤ縦型サラウンディングゲートトランジスタの作製

Demonstration of InP nanowire vertical surrounding-gate transistor (1.北海道大学工学部、2.北海道大学情報科学研究科および量子集積センター) O勝見 悠 <sup>1</sup>、蒲生 浩憲 <sup>2</sup>、佐々木 正尋 <sup>2</sup>、本久 順一 <sup>2</sup>、冨岡 克広 <sup>2</sup>、

(1.Hokkaido Univ., 2.Graduate School of IST and RCIQE, Hokkaido Univ.)

°Yu Katsumi<sup>1</sup>, Katsuhiro Tomioka<sup>2</sup>, Masahiro Sasaki<sup>2</sup>, Hironori Gamou<sup>2</sup>, Junichi Motohisa<sup>2</sup>

E-mail:katsumi@rciqe.hokudai.ac.jp

[はじめに] 電界効果トランジスタ(FET)は、そ の微細化にともない集積回路における集積度 の向上、低消費電力化、高速動作化を同時に実 現してきた。しかし、現行の微細化技術は、 物理的なサイズ限界と熱力学的な物理限界に よって、上記の利点が失われつつある。この課 題を克服するため、III-V 族化合物半導体に代 表される高移動度チャネル材料や立体ゲート 構造が検討されている。III-V 族化合物半導体 は、移動度の高さからオン電流を増大させ、低 駆動電圧下でのデバイス動作を可能にし、消費 電力削減に寄与する。また、立体ゲート構造は オフリーク電流を抑制し、消費電力を低減でき る。III-V 族化合物半導体ナノワイヤのうち、 InP ナノワイヤは、ウルツ鉱型単結晶構造を作 製することができ、ウルツ鉱に起因した原子的 に平坦なファセット面を金属-酸化物-半導体 (MOS)界面に利用できるメリットがある[1]。本 報告は、InP 基板上に選択成長した InP ナノワ イヤの縦型サラウンディングゲートトランジ スタ(SGT)作製について検討した。

[実験方法] n型 InP(111)A 基板に、RF スパッタリング法により膜厚 18 nm の  $SiO_2$  を堆積させた。この基板に電子線リソグラフィー、ウェットエッチングを用いて開口部を形成し、有機金属気相選択成長(SA-MOVPE)法により InP ナノワイヤを成長した。成長原料は、III 族原料にtrimethyl indium(TMIn)、また V 族原料にtertiarybutylphosphine (TBP)を用いた。成長条件は成長温度  $660^{\circ}$ C とし、Zn パルスドープ層を 5 分 30 秒成長した後、Si ドープ層を 3 分成長させた。V/III 比は 24 とした。

次に、原子層堆積法によりゲート酸化膜として HfAlO 膜を堆積させ、スパッタリング法によりゲート電極として W を成膜した。次に、スピンコーティングにより benzocyclobutene (BCB)でナノワイヤを包埋し、反応性イオンエッチングでナノワイヤ上部のゲート電極と HfAlO 膜をエッチングし、ゲート構造を作製した。最後に、BCB でゲート・ドレイン間分離層を形成しドレイン・ソース電極を堆積した。

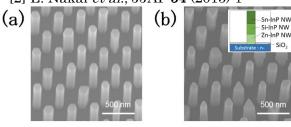

[結果]図 1(a)にアンドープ InP ナノワイヤの

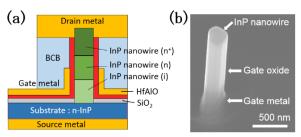

Scanning Electron Microscope(SEM)像を、(b)に ドーピングを行った InP ナノワイヤの SEM 像 を示す。図1より、ドーピングの有無によらず InP ナノワイヤは{-110}垂直ファセットと (111)A で囲まれており、垂直ファセットはへ き開面から 30°回転していることからナノワ イヤの結晶構造がウルツ鉱型結晶構造である ことがわかる[1]。ナノワイヤの高さが 1000 nm 以上のものでその形状を比較すると、アン ドープのナノワイヤは平均直径が 119.5 nm、 ドーピングを行ったナノワイヤの平均直径は 112.5 nm であった。これは、パルスドーピン グを行うことでドーピングによる横方向成長 が抑制されたと考えられる[2]。次いで、図 2(a),(b)に InP ナノワイヤ縦型 SGT の模式図と 作製した素子構造の SEM 像を示す。ナノワイ ヤの垂直ファセット全面にゲート電極・酸化物 が堆積し、図 2(a)の縦型サラウンディングゲー ト構造が作製されていることがわかる。

当日は、この素子のスイッチング特性などについて議論する。

## [参考文献]

[1] Y. Kitauchi *et al.*, Nano Lett. **10** (2010) 1699-1703

[2] E. Nakai et al., JJAP **54** (2015) 1

図 1.(a)アンドープ InP ナノワイヤ SEM 像 (b)ドープした InP ナノワイヤ SEM 像

図 2.(a)InP ナノワイヤ縦型 SGT の模式図 (b)作製した素子の SEM 像