# C2W 三次元集積のための自己組織化静電仮接合の評価

**Evaluation of Self-Assembly and Electrostatic Temporary Bonding for Chip-to-Wafer 3D Integration**

東北大院工1. 東北大未来研2. 東北大院医工3.

o橋口 日出登<sup>1</sup>,福島 營史<sup>2</sup>,裵 志哲<sup>2</sup>,木野 久志<sup>1</sup>,李 康旭<sup>2</sup>,田中 徹<sup>1,3</sup>,小柳 光正<sup>2</sup> Dept. of Bioengineering and Robotics<sup>1</sup>, NICHe<sup>2</sup>, Dept. of Biomedical Engineering<sup>3</sup>, Tohoku Univ.

<sup>°</sup>H. Hashiguchi<sup>1</sup>, T. Fukushima<sup>2</sup>, J.-C. Bea<sup>2</sup>, H. Kino<sup>1</sup>, K.-W. Lee<sup>2</sup>, T. Tanaka<sup>1,3</sup>, and M. Koyanagi<sup>2</sup> E-mail: link@lbc.mech.tohoku.ac.ip

#### 1. 諸言

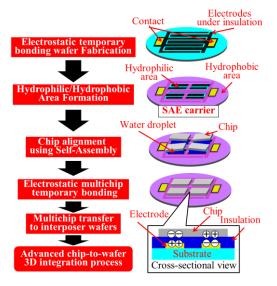

近年、半導体集積回路(IC: Integrated circuit)の素子及び配 線の微細化に伴い、信号遅延・消費電力増大などの問題が 顕在化している。そうした中、複数の IC を積層し、各層 を Through-Silicon-Via (TSV)及び金属マイクロバンプによ り電気的に接続する三次元集積化技術が注目されている。 これにより、三次元的に素子や配線を集積することで、微 細化に依らない高集積化を実現する事ができる。IC の積 層には、チップレベルまたはウェハレベルで積層する方式 に比べ、チップをウェハ上に積層する Chip-to-Wafer(C2W) 積層が有効である。C2W 積層では、良品チップを選別し て積層し、ウェハ上のチップを一括で三次元集積すること が可能なため、高生産性と高歩留りを両立することができ る。これまで我々は、Fig.1 に示すように、水滴を駆動力 とした高速、高精度チップ位置合わせ技術であるチップ自 己組織化搭載技術と[1]-[4]、さらに搭載したチップをウェ ハ上に一時的に接合する静電仮接合技術を組み合わせた 自己組織化静電仮接合(SAE: Self-assembly and electrostatic temporary bonding)技術を提案してきた[5]-[7]。この技術の 特徴は、SAE キャリア上の電極に電圧を印加することでチ ップ-キャリア間に生じる静電接合力が電源を取り外した 後も持続するため、SAE キャリアをチップのハンドリング 基板として、C2W 三次元集積を行うプロセス装置に搬入 できる点である。

本研究では、チップ静電仮接合時の接合力を引張試験器によって実際に測定した。このようにして測定した接合力と各工程でチップに加わる外力の関係を求めることにより、プロセス中に生じるチップの位置ずれを予測することが可能となる。

## 2. 実験

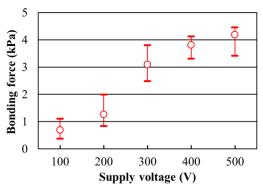

本実験では、SAE キャリア上で静電仮接合したチップの接合力を引張試験器により測定した。SAE キャリアには歯幅 500µm、厚さ1µm、ピッチ1mmのバイポーラ型櫛歯電極が形成されており、表面には厚さ6µmの酸化膜をプラズマ励起型化学気相成長法により成膜している。キャリア上に静電仮接合するチップは30mm×30mm角、厚さ280µmのサイズで、基板はSiである。チップ表面にはスタッドピンを固定しており、引張試験器を用いてこのピンを引き上げることで、チップに生じる静電仮接合力を測定した。このとき、バイポーラ型電極に電源を接続し、100-500Vの電圧を印加してチップの静電仮接合を行っている。3. 結果

Fig. 2 に接合力の測定結果を示す。図から明らかなように、チップには数 kPa 程度の接合力が生じている。これは、ハンドリング中に様々な外力によってチップが基板から剥離しない十分な接合力である。本研究ではさらに、静電仮接合したチップに水平方向の力を与えた場合についても評価しており、発表ではこれらの結果についても詳述する

# 謝辞

本研究の一部は科学研究費補助金 基盤研究(S) (21226009)の助成を受けたものである。

### 参考文献

- [1] T. Fukushima et al., IEDM Tech. Dig., (2005) 359.

- [2] T. Fukushima et al., IEDM Tech. Dig., (2007) 985.

- [3] T. Fukushima et al., IEDM Tech. Dig., (2009) 349.

- [4] T. Fukushima et al., Proc. of ECTC, (2010) 1050.

- [5] T. Fukushima et al., IEDM Tech. Dig., (2012) 789.

- [6] H. Hashiguchi et al., Proc. of SSDM, (2012) K-4-3.

- [7] H. Hashiguchi et al., Proc. of ICEP, (2013) FA2-4.

Fig. 1 SAE technology for chip-to-wafer 3D integration

Fig. 2 Relationship between electrostatic bonding force and supply voltage