## ALD-Al<sub>2</sub>O<sub>3</sub> 絶縁体層を有する InAIN MOS ダイオードの作製手順の検討 Study on Fabrication Sequence of InAIN MOS Diodes with ALD-Al<sub>2</sub>O<sub>3</sub> Insulator Layer 北大量集センター <sup>○</sup>千葉 勝仁, 中野 拓真, 赤澤 正道

RCIQE, Hokkaido Univ. OMasahito Chiba, Takuma Nakano, Masamichi Akazawa E-mail: chiba@rciqe.hokudai.jp

【はじめに】InAIN/GaN HEMT の遮断周波数は、ゲート絶縁膜の導入により向上し、400GHz に達している  $^{1)}$ 。しかし、絶縁膜/InAIN 界面の特性が、デバイスの作製工程により、どのような影響を受けるかについては未知の部分が多い。ここでは、 $ALD-Al_2O_3$  絶縁膜を有する InAIN MOS ダイオードについて、熱処理を含む作製手順の違いが  $Al_2O_3$  /InAIN 界面特性にどのような影響を与えるかを調べた結果を報告する。

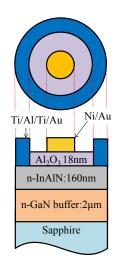

【実験】図 1 に示す構造を有する  $InAlN(n-In_{0.17}Al_{0.83}N, n=2\times10^{18}cm^3)$  MOS ダイオード試料 A,B,C を、異なる作製手順により作製し、C-V 測定と界面準位の評価を行った。絶縁膜である  $Al_2O_3$  は、 $H_2O$  と TMA を用いた ALD 法により堆積した。また、オーミックアニールは  $N_2$  中 850°C で 1 分間 行った。

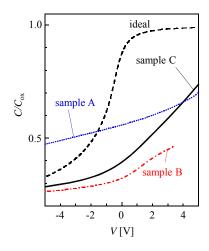

【結果】試料 A については、厚さ 18nm の  $Al_2O_3$  膜を形成後にオーミックアニールを行った。1MHz での C-V 測定結果は変化量が小さく(図 2)、評価ができる範囲内での界面準位密度は高い値となった (図 3)。  $Al_2O_3$  層形成後に高温で熱処理することが特性を悪化させた可能性がある。次に、試料 B は  $Al_2O_3$  層堆積前に、表面保護膜を用いずにオーミックアニールを行って作製したが、良好な C-V 特性は得られなかった(図 2)。この試料に関しては表面フェルミ準位がバンドギャップの深い位置に入りこんでしまっているために、界面準位の評価は難しいが、C-V 特性は高密度の界面準位の存在を示している。また、キャップレスアニールにより表面の酸化が進行したことを XPS で確認した。これらの結果を踏まえて、試料 C においては、オーミックアニールの際に InAIN 表面を SIN 膜で保護し、BHF によって SIN 膜を除去してから  $Al_2O_3$  を堆積させた。試料 C の C-V 特性は、他の試料に比べて最も容量値の変化が大きく (図 2)、また、界面準位密度は図 SIN に大幅に低減した。以上の結果から、SIN 膜を保護膜とするオーミックアニールを行うことが適切であることがわかった。

1) Y. Yue et al., presented at IWN2012, Sapporo, Oct.14-19.2012.

Fig.1 Structure of MOS diodes.

Fig.2 C-V curves measured at 1MHz with ideal curve.

$\begin{array}{lll} Fig.3 & D_{it} & disturibution & evaluated \\ from & C-V & curves & using & high \\ frequency & method. \end{array}$