## 大気圧マイクロ熱プラズマジェット結晶化を用いた 微細薄膜トランジスタの特性評価

Characteristic Evaluation of fine TFTs Crystallized by Micro Thermal Plasma Jet Irradiation 広大院先端研

誠司,林 将平,上倉 敬弘,山本 将吾,赤澤 宗樹,酒池 耕平,東 清一郎 Graduate School of Advanced Sciences of Matter, Hiroshima University S.Morisaki, S. Hayashi, T.Kamikura S.Yamamoto, M.Akazawa, K.Sakaike and S. Higashi E-mail: semicon@hiroshima-u.ac.jp

序>これまで我々は、マイクロ熱プラズマジェット(μ-TPJ) を用いた高速横方向結晶化(HSLC)の制御を行い、大粒径の 結晶成長を報告し[1]、高性能の薄膜トランジスタ(TFT)特性 [2]、さらに a-Si 細線を用いた結晶成長の位置制御によりば らつきを低減して CMOS 回路の駆動を実証してきた[3]。さ らに TFT を微細化することで、チャネル領域の単結晶化に よりさらに高速、高集積の回路が期待される。本研究では、 高結晶性のSiを用いて短チャネルTFTの特性を詳しく調査 し、回路作製の指針を得た。

実験>石英基板上に PECVD 法を用いて 200nm の a-Si を堆 積し、450℃の脱水素処理を行った。続いて大気圧下におい て Ar ガス流量(f)2slm、投入電力(P)1.6kW、噴出口径 600μm より発生した μ-TPJ の前面 1mm において、速度 (v)2100mm/sec で基板を走査して a-Si を結晶化した。ここで、 単一グレインでの TFT 形成を狙い、チャネル長(L)2~10μm 、

幅(W)=3μm で TFT を形成した。その後[3]同様に、 自己整合トップゲート構造の TFT を作製した。TFT 形成後に、水素アニール(PMA)の温度を 250°C から -400°C まで 50°C 毎に変化させて、NMOS、PMOS 両 TFT 特性の変化を調べた。

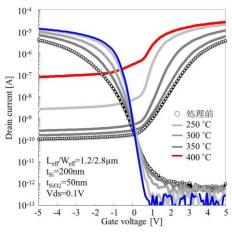

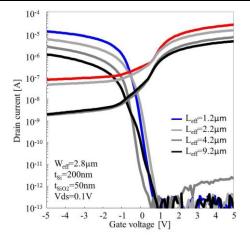

結果および考察>最初に TFT 特性を正確に調べるため、同 一基板上の酸化膜容量と実効チャネル長(L<sub>eff</sub>)を求め、TFT 特 性を評価した。HSLC では~60μm のグレインが形成されるこ とから[1]、L<sub>eff</sub>/W<sub>eff</sub>=1.2/2.8μm 作製した TFT は単一グレイン でチャネル形成されていると考えられる。Fig.1 に示すよう に、NMOS は PMA により、移動度、しきい値が向上したの に対し、オフ電流  $I_{\text{off}}$  が増加した。これに対し PMOS では、 PMA 温度に対してすべての特性が向上し、Ioff も改善された。 Table.1 に示すように、HSLC で形成された TFT は単結晶同 等の移動度を示していることから、NMOS の Iof の増加は HSLC の高結晶性によると考えられ、チャネル領域は極めて 結晶性が高く、僅かに natural-n type であると考えられる。さ らに Fig.2 に示すように、Iof を含む TFT 特性が長チャネルに おいても同様の傾向を示した。このことから、a-Si 細線パタ Fig.2 TFT 伝達特性の実効チャネル長依存性。

Fig.1 L<sub>eff</sub>/W<sub>eff</sub>=1.2/2.8μm の NMOS および PMOS 伝達特性の水素処理温度依存。

| Table.1 L <sub>eff</sub> /W <sub>eff</sub> =1.2/2.8μm の TFT 伝達特性。 |          |             |          |                    |

|-------------------------------------------------------------------|----------|-------------|----------|--------------------|

|                                                                   | $V_{th}$ | $\mu_{FE}$  | S-factor | $I_{\mathrm{off}}$ |

|                                                                   | (V)      | $(cm^2/Vs)$ | (mV/dec) | (A)                |

| NMOS                                                              | 0.80     | 541         | 684      | 5.2e-8             |

| PMOS                                                              | -0.68    | 217         | 173      | $<1.0e^{-13}$      |

ーンを用いた結晶成長位置制御を行うことでばらつきを抑え[3]、短チャネル TFT を用いた回路の高速 駆動が期待できる。

**結論>μ-TPJ** 結晶化による欠陥密度の極めて少ない結晶性を確認し、a-Si 細線構造を用いた結晶成長制 御の位置制御より微細 TFT を用いた回路形成の見通しができた。

**謝辞>**本研究の一部は、広島大学ナノデバイス・バイオ融合科学研究所の施設を用い、最先端・次世 代研究開発支援プログラム(NEXT プログラム)の支援の下に行われた。

- [1] S.Higashi et al: J. Appl. Phys. **50** (2011) 03CB10.

- [2] S.Hayashi et al: Appl. Phys Express 3 (2010) 061401.

- [3] 森崎他, 第60回応用物理学春季学術講演会 (2013年春季)162, 29p-B8-7.