## 高温熱処理を挟む2段階ALDプロセスによるAl<sub>2</sub>O<sub>3</sub>/InAIN界面特性の向上

Improvement of Al<sub>2</sub>O<sub>3</sub>/InAlN interface properties through two-step ALD process interrupted by high-temperature annealing

## 北大量集センター, 情報科学研究科 〇中野 拓真, 千葉 勝仁, 赤澤 正道

RCIQE and Graduate School of Information Science and Technology, Hokkaido Univ.

°Takuma Nakano, Masahito Chiba, Masamichi Akazawa

E-mail: tnakano@rciqe.hokudai.ac.jp

【はじめに】格子整合系 InAIN/GaN ヘテロ界面は、高い電子障壁を有し、大きな自発分極差により高密度の 2 次元電子ガスを発生させることができる。最近では InAIN が InAIN

【実験方法】図 1 は試料作製プロセスの模式図である。オーミックコンタクト形成後、適切な処理を施し ALD により 2 nm の極薄  $Al_2O_3$ 層を堆積し、 $N_2$ 雰囲気中 850°C1 分間アニールを行った。その上に再び ALD により 16 nm の  $Al_2O_3$ 層を堆積し NiAu 電極を蒸着した。比較のためオーミックアニール後、ALD により 18 nm の  $Al_2O_3$ 層を一度に堆積し、NiAu 電極蒸着前にアニールを行った試料と行っていない試料の 2 つを作製した。

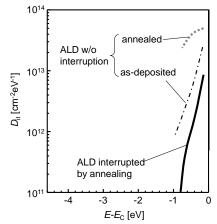

【実験結果】XPS により、アニール温度 950℃に対しても界面構造の乱れが引き起こされた兆候は見られないことを確認した。しかし、ヘテロ界面への影響は調べていないので、アニール温度としてはオーミックアニール温度である 850℃に設定した。各試料の 1 MHz での C-V 特性を図 2 に、界面準位密度分布の評価結果を図 3 に示す。一度に  $Al_2O_3$  を堆積した試料はアニールにより C-V 特性が劣化し、界面準位密度が増加した。これまでの報告[2,3]を参考にすると、 $Al_2O_3$  バルク中に結晶粒界が発生することにより、特性が劣化した可能性が大きい。そこで界面付近のみアニールする 2 段階 ALD プロセスを試みた。その結果、C-V 特性が大きく改善され、界面準位密度も大幅に低減されることを確認した。

- [1] Y. Yue et al., presented at IWN 2012 (Sapporo, Oct. 14-19, 2012).

- [2] Y. Q. Wu, T. Shen, P. D. Ye, G. D. Wilk, Appl. Phys. Lett. 90, 143504 (2007).

- [3] Y. Hori, C. Mizue, and T. Hashizume, Jpn. J. Appl. Phys. 49, 080201 (2010)

Fig 1 Fabrication process.

Fig 2 C-V curves.

Fig 3  $D_{it}$  distribution evaluated from C-V curves.