## ゾルゲル法を用いたガラス基板上 酸化亜鉛系透明薄膜トランジスタの作製

Fabrication of zinc oxide transparent thin film transistors on glass substrates by sol-gel method 大阪工業大学 ナノ材料マイクロデバイス研究センター 〇佐々木 悟, 前元 利彦, 尾形 健一, 佐々 誠彦

Nanomaterials Microdevices Research Center, Osaka Institute of Technology

Os. Sasaki, S. Sasa, K. Ogata and T. Maemoto

E-mail: m1m12313@st.oit.ac.ip

【はじめに】酸化亜鉛 (ZnO) は塗料や化粧品にも使われており、環境や人体に対しても比較的影響が少ないという特長がある。また電子デバイス材料としては、3.3 eV の禁制帯幅を持つ可視光領域で透明なワイドギャップ半導体であり、室温成膜が可能なためプラスチックなどのフレキシブル基板上へのデバイス応用が期待できる。他方、ゾルゲル法による溶液を用いた電子デバイスの作製技術は、薄型で軽量、柔軟性を持つ電子デバイス作製の省資源、省エネルギー製造を可能にする技術として期待されている。ゾルゲル法の特徴として、真空装置が不要である、環境にやさしいプロセスで簡易な手法によって大面積化にも対応できるなどが挙げられる。

今回,我々はゾルゲル法を用いて ZnO 系薄膜を作製し,In 添加したときの薄膜の結晶性を評価するとともに,薄膜トランジスタ (TFT) のプロセス開発と特性評価を行ったのでそれらの結果について報告する.

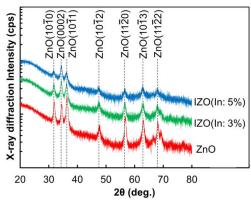

【実験と結果】モノエタノールアミン,2-メトキシエタノール,酢酸亜鉛 2 水和物とを混合し,0.25 mol/l の濃度で前駆体溶液を作製した.またシート抵抗値の低減化のために,In を添加する場合は塩化インジウム 4 水和物を混合し,50℃で 3 時間撹拌することでゾルゲル溶液を得た.この ゾルゲル溶液をスピンコーティング法によりガラス基板 (イーグル XG) に塗布し,電気炉を用いて 500℃で 4 時間焼結を行うことで 60 nm の ZnO 薄膜を形成した.作製した ZnO 薄膜および In 添加 ZnO 薄膜の結晶性を評価するために XRD 測定を行った.その結果を図 1 に示す.In 添加量 の増加に伴い,回折ピーク強度は減少したが,c 軸方向の ZnO (0002)面の他に様々な結晶面からの回折ピークが観測されたことから,多結晶薄膜が得られていることが分った.

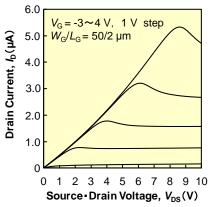

次に ZnO 薄膜を用い、フォトリソグラフィにより、幅  $W_G=50~\mu m$ 、ゲート長  $L_G=2~\mu m$  をもつトップゲート型 ZnO-TFT に加工し、ソース・ドレイン間電圧ードレイン電流( $V_{DS}$ - $I_D$ )特性を評価した.その結果を図 2 に示す.伝達コンダクタンス  $g_m$  は 51.9  $\mu$ S/mm,ON/OFF 比は 2.6×10<sup>6</sup> と、ガラス基板上の TFT で明瞭なトランジスタ動作を確認した.

当日は In 添加した ZnO 膜の透過測定, AFM 像による表面粗さ測定および XPS 測定による In 添加量の算出, TFT の出力特性および伝達特性について詳しく報告する.

[1] Y. Fujihara et al., 24th International Microprocesses and Nanotechnology Conference (2011).

図 1 In 添加量を変化させた IZO 薄膜からの XRD 回折パターン

図 2 作製した ZnO-TFT の V<sub>DS</sub>-I<sub>D</sub> 特性