## 緩衝層が GaN 接合特性に与える影響

Effects of buffer layers on GaN-based junction properties 北大量集センター 情報科学研究科 <sup>1</sup>, JST-CREST <sup>2</sup> ○馬 万程 <sup>1</sup>, 堀 祐臣 <sup>1</sup>, 谷田部 然治 <sup>1</sup>, 橋詰 保 <sup>1,2</sup>

RCIQE, Graduate School of Information Science and Technology, Hokkaido Univ.<sup>1</sup>, JST-CREST<sup>2</sup>

"Wan-Cheng Ma<sup>1</sup>, Yujin Hori<sup>1</sup>, Zenji Yatabe<sup>1</sup>, and Tamotsu Hashizume<sup>1,2</sup>

E-mail: ba@rciqe.hokudai.ac.jp

【はじめに】異種基板上に GaN 系デバイスを形成する場合、活性層を成長する前に、低温成長層・超格子層などの複雑な緩衝層を用いる場合が多い。このような緩衝層は、活性層との界面に種々の結晶欠陥を誘起したり、あるいは電子捕獲・電子蓄積の要因となる可能性を持っているが、その影響は明らかになっていない。本報告では、GaN自立基板上に AlGaN/GaN 超格子層を含む n-GaN層を形成し、ショットキー接合および MOS 接合のポテンシャル制御に、超格子層がどのように影響するかを調べたので報告する。

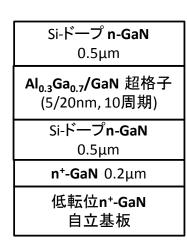

【実験と結果】図 1 に、試料構造の模式図を示す。低転位密度の n-GaN 自立基板上に  $n^+$ -GaN および n-GaN を成長した。引き続き、 $Al_{0.3}Ga_{0.7}N(5nm)/GaN(20nm)$  の超格子構造を 10 周期成長し、最後に n-GaN を  $0.5\mu m$  成長した。成長は MOCVD で行い、n-GaN 層には Si をドーピングした。この構造表面に、Ni/Au ゲートによるショットキー接合と  $Ni/Au/Al_2O_3(20nm)$ による MOS 接合を形成した。 $Al_2O_3$  膜の堆積は、純水と TMA を原料とする ALD により行った。

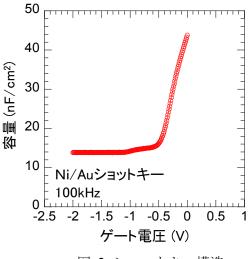

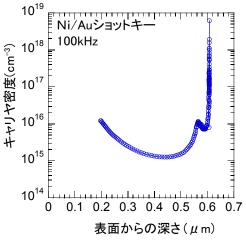

図 2 にショットキー接合の 100kHz での C-V 特性を示す。逆バイアスの印加とともに容量は減少するが、-0.5V 付近で C-V 曲線の傾きが緩やかになり、-1V 以降ではほぼ一定の容量を示した。この C-V 特性より計算したキャリア密度分布を図 2 に示す。最表面の n-GaN 領域では、 $10^{15}$ ~  $10^{16}$ cm<sup>-3</sup> のキャリア密度分布であるが、AlGaN/GaN 超格子層の領域において急激な密度の増加が見られ、顕著なキャリア蓄積が生じていることが推定される。このキャリア蓄積と AlGaN 層の伝導帯バリアにより、逆バイアスを増加させても空乏層の拡がりが阻害されるものと思われる。MOS 接合特性においても、同様の空乏層のふるまいが観測された。

図 1 緩衝層を導入した n-GaN の試料構造

図 2 ショットキー構造 の C-V 特性

図 3 n-GaN 表面からの キャリヤ密度分布