## Formation of sub-10nm nanoholes by two-step anodization of aluminum on silicon substrate

Van Hoang NGUYEN<sup>1,2</sup>, Haruna WATANABE<sup>1,2</sup>, Noritaka USAMI<sup>1,2</sup>

Institute of Materials Research, Tohoku University<sup>1</sup>

FUkushimaTop-level United center for Renewable Energy (FUTURE), JapanScience and Technology agency (JST)<sup>2</sup>

## Abstract

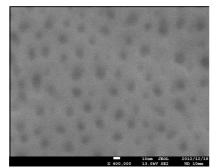

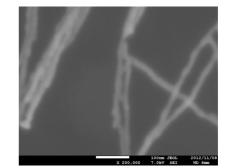

Arrays of silicon nanowires are promising for electronic[1] and opto-electronic[2] applications thanks to large surface to volume ratio as well as quantum size effect. Among various methods to fabricate silicon nanowires, vapor-liquid-solid (VLS) growth is one of the most popular techniques that require the use of a metallic catalyst. Gold is the most selected one due to low Si-Au eutectic temperature. However, the distribution of gold catalystis almost randomly dispersed on silicon substrate. Using the anodic aluminum oxide (AAO) via electrochemical gold deposition on silicon substrate is referred to improve the homogeneous distribution of gold catalyst. The pore diameters ofAAO control the size of gold catalystas well as thediameter of the subsequently grown silicon nanowires. In this contribution, we will focus onself-ordered AAO templatefabrication on silicon substrate using well-known two step anodizing process in sulphuric acid electrolyte. By monitoring the anodization current during the electrochemical process as a function of time, the pore diameters of AAO were controlled.Small pore diameters in range of about 8-20nm were obtained by applying a low anodizing potential5-12V [Figure 1a]. Further working is aimed to deposit gold molecules inside the sub-10nm cylinder structure of AAO template by electrochemical plating method. Gold nanowires with sub-10nm diameter are formed by firstly proceeding long plating duration and subsequently using chemical wet etching with AAO template [Figure 1b].

**Figure 1:**SEM images depicting:**a**) AAO template fabricated at anodized voltage 6V; **b**)gold nanowires formed at plating voltage 3V.

## References

[1] Akram I. Boukai, Yuri Bunimovich, JamilTahir-Kheli, Jen-Kan Yu, William A. Goddard III, James R. Heath, Nature451 (2008) 171, *Silicon nanowires as efficient thermoelectric material.*

[2] JeeEun Yang, Chang-Beom Jin, CheolJoo Kim, Moon Ho Jo, Nano Letters, 6(2006) 2684, Band gap modulation in single crystalline Sil-xGex nanowires.