# シリコン基板上に作製した PZT 薄膜積層アクチュエータ

PZT multilayer thin films actuator fabricated on Si substrate 神大院工¹,京大院工² ○岸本 真哉¹,黒川 文弥²,神野 伊策¹

Kobe Univ. 1, Kyoto Univ<sup>2</sup>, Masaya Kishimoto<sup>1</sup>, Fumiya Kurokawa<sup>2</sup>, Isaku Kanno<sup>1</sup>

E-mail: 121t320t@stu.kobe-u.ac.jp

## 1. はじめに

近年、電子デバイスの小型化、高性能化に伴い、積層セラミックコンデンサ (MLCC) や圧電積層アクチュエータ (MLCA) などの積層セラミックスの小型化、集積化が進められている。MLCC及び MLCA は、誘電体及び圧電体と内部電極を交互に積層し両端に外部電極を取り付けた構造を持つ、従来、MLCC、MLCA はテープキャスティング法により作製されてきた[1]. しかし、大きな比誘電率を有する誘電体をサブミクロンオーダーの膜厚で作製することは容易ではない。一方、スパッタ法、Chemical Vapor Deposition (CVD) 法などの気相薄膜成長法は、強誘電性を有する薄膜をサブミクロンの膜厚で作製することが可能である。さらに、Si 基板上に誘電体を成膜できるため、半導体材料への機能性材料の集積化も可能である。しかし交互に配置された内部電極を有する薄膜を作製することは容易ではなく、実用的な積層構造作製法は未だ確立されていない。そこで、気相薄膜成長法のみを用いて、外部・内部電極層と誘電体層を一括形成する簡易な積層構造作製法の確立が必要である。これまで我々は MLCC 応用を目的としてスパッタ法を用いて誘電体薄膜を作製し、その誘電特性について報告してきた[2]。

今回、積層アクチュエータへの応用として PZT 積層薄膜を Si 基板上に作製し、その結晶構造、電気特性及び圧電特性を評価した.

#### 2. 実験方法

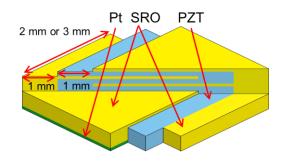

PZT 積層薄膜は、RF マグネトロンスパッタリング法を用いて Si 基板上に成膜した. 内部電極が一層ごと交互に 1 対の外部電極と接続している構造を一括して作製するため、基板上に可動マスクを設置し、PZT 層(Zr/Ti=53/47)および内部電極の成膜前後にマスクを移動させて成膜した. 内部電極として導電性酸化物である  $SrRuO_3$  (SRO) を使用した. PZT 及び SRO の膜厚はそれぞれ約500 nm 及び 80 nm である. なお、SRO の結晶性、密着性を向上させるために、Si 基板上の SRO 電極との界面には Pt を成膜した. 今回、PZT 圧電体層数を 1、3、及び 5 層とした各積層薄膜を作製した.

### 3. 結果·考察

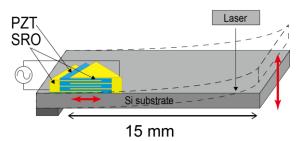

作製した積層構造の断面の模式図を Fig.1 に示す. 作製した PZT 積層膜の結晶構造は X 線回析 (XRD) により評価した結果,ペロブスカイト構造の PZT 積層膜が形成されていることが確認できた. また, PZT 積層膜の比誘電率は積層数に関わらず 1100 程度と一定であり,単位面積あたりの静電容量は積層数にほぼ比例していた. PZT 積層薄膜の圧電特性は Fig.2 のようにカンチレバー状にサンプルを切り出し,圧電横効果による先端変位をレーザードップラー振動計で測定した.

#### 参考文献

- [1] R. E. Mistler, el al., Tape Casting: Theory and Practice. Westerville: The American Ceramic Society, 2000.

- [2] Y. Imamiya, et al., Jpn. J. Appl. Phys. 50 (2011) 09NA01

Fig. 1 Schematic cross section of multilayer thin films.

Fig. 2 Schematic illustration of PZT multilayer unimorph cantileyer.