28p-G11-6

## Field Isolation of GaN MOSFET by Boron Ion Implantation

The Univ. of Tokushima<sup>1</sup>, Dalian Univ. of Tech.<sup>2</sup>, Kyushu Inst. of Tech.<sup>3</sup>, SAMCO Inc.<sup>4</sup> <sup>°</sup>Ying Jiang<sup>1,2</sup>, Qingpeng Wang<sup>1,2</sup>, Kentaro Tamai<sup>1</sup>, Satoko Shinkai<sup>3</sup>, Takahiro Miyashita<sup>4</sup>, Shin-Ichi Motoyama<sup>4</sup>, Dejun Wang<sup>2</sup>, Jin-Ping Ao<sup>1</sup>, and Yasuo Ohno<sup>1</sup>

E-mail: yjiang@ee.tokushima-u.ac.jp

GaN MOSFETs are being developed to achieve enhancement-mode (E-mode) operation [1]. However, the device isolation is still not developed. The region is called "field region" and should be non-conductive even in case of high voltage wiring running over the region. In this paper, we report the investigation on the device isolation processes for GaN MOSFETs by three technologies, boron ion implantation (B I/I), Ni diffusion and reverse sputtering treatment.

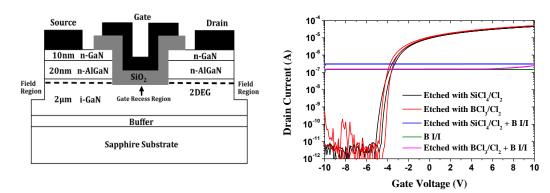

GaN MOSFETs were fabricated on AlGaN/GaN heterostructure where gate region is formed by the removal of the AlGaN layer (Fig. 1). Ring-type MOSFETs with inner and outer gate electrode radii of 89  $\mu$ m and 183  $\mu$ m (L=94  $\mu$ m, W<sub>eff</sub>=819  $\mu$ m) were used for the conductivity evaluation. There are two patterns on the chips, normal gate MOSFET and field MOSFET. In the fabrication process, field isolation was first done with different isolation conditions, which were ICP dry etching with the gases of  $SiCl_4/Cl_2$  or  $BCl_3/Cl_2$ . with or without B I/I, Ni diffusion and reverse Ar sputtering in sputtering chamber. After the etching, B ions were double implanted to some samples with the energy, dose of 30 keV,  $5 \times 10^{14}$  cm<sup>-2</sup> and 110 keV,  $7 \times 10^{14}$  $cm^{-2}$ , respectively. The mask for I/I was the double layers of 500 nm SiO<sub>2</sub> and 2  $\mu$ m photoresist. For another samples, 100 nm thick Ni was sputtered, lifted-off and annealed at 850 °C for 30 min in N<sub>2</sub> ambient as drive-in diffusion. Then, Ni was removed by aqua regia. The reverse sputtering treatment with Ar plasma was done for 30 min with the power of 180 W. Then, the gate region was etched by ICP with SiCl<sub>4</sub> at a lower etching rate to reduce the etching damage. After gate region etching, silane-based SiO<sub>2</sub> (100 nm) was deposited as gate oxide for both normal gate and field FETs, and annealed at 1000 °C for 10 min in  $N_2$ ambient. The ohmic contacts were formed using Ti/Al/Ti/Au (50/200/40/40 nm) annealed at 850 °C for 1 min in  $N_2$  ambient. The gate metal was formed using Ni/Au (70/30 nm) both for normal gate and filed FETs again.

The devices of normal gate FETs demonstrated an electron mobility of about 140 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [1]. The field FETs without any special treatments showed E-mode operation (Fig. 2) with electron mobility of about 120 and 135 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for the devices etched with SiCl<sub>4</sub> and BCl<sub>3</sub>, respectively. The devices with Ni diffusion and reverse sputtering had large oxide leakage and cannot be measured the transistor characteristics. The devices with boron ion implantation showed low drain currents and no change with the gate bias. In addition, no deterioration of electron mobility and no threshold voltage variation were observed from the normal gate FETs on the same chips.

In conclusion, B I/I is an effective method to obtain good device isolation for GaN MOSFETs.

Fig. 1 Device structure of GaN MOSFETs

## Fig. 2 Transfer characteristics of ring-type MOSFETs formed in field region.

## References

[1] Q. Wang: Jpn. J. Appl. Phys 52, (2013) (in press).