## Mobility Degradation of Ge MOSFETs in High N<sub>s</sub> Region due to Interface States inside Conduction and Valence Bands of Ge

Rui Zhang, Po-Chin Huang, Ju-Chin Lin, Mitsuru Takenaka and Shinichi Takagi

The University of Tokyo, 2-11-16 Yayoi, Bunkyo-ku, Tokyo 113-8656, Japan Email: <u>zhang@mosfet.t.u-tokyo.ac.jp</u>

**Introduction** Ge has been attracting a lot of interests as one of future high mobility channel materials to further enhance the performance of present Si MOSFETs <sup>[1]</sup>. Although high peak mobility has already been realized for Ge MOSFETs by employing thermal oxidation <sup>[2-4]</sup> and plasma post oxidation <sup>[5, 6]</sup>, it is typically observed that the effective mobility in Ge MOSFETs severely degrades in the high N<sub>s</sub> or normal field region. The mechanism of this high N<sub>s</sub> mobility degradation is still not clear yet.

In this study, Hall measurements are carried out to systematically study the degradation mechanism of the mobility in both Ge p- and n-MOSFETs with different substrate orientations and interface qualities. It is found that the effective mobility in Ge MOSFETs is significantly reduced in high  $N_s$  through the loss of induced surface carrier density in the channels of p- and n-MOSFETs due to interface states inside the valence band (VB) and conduction band (CB) of Ge, respectively.

**Experiment** Subsequent to the cleaning of Ge (100) wafers, SiO<sub>2</sub> field oxide was formed on Ge substrates and the active areas were defined. After ion implantation of source/drain regions and activation annealing, the GeO<sub>x</sub>/Ge interface was fabricated by plasma post oxidation of 1-nm-thick Al<sub>2</sub>O<sub>3</sub>/Ge structures at 300 °C. A 2<sup>nd</sup>-ALD deposition of 5-nm-thick Al<sub>2</sub>O<sub>3</sub> was carried out to suppress the gate leakage. PDA was performed at 400 °C for 30 min in N<sub>2</sub>. TiN gate stacks were sputtered and patterned. Finally, Al was deposited for source/drain and back electrode contacts.

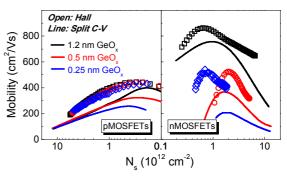

**Results and discussion** The normal operations of the Ge p- and n-MOSFETs have been confirmed from the  $I_d$ -V<sub>g</sub> characteristics (data not shown). The mobility of these Ge MOSFETs was evaluated by both the split C-V method and the Hall measurements. As shown in Fig. 1, hole and electron Hall mobility are much higher for both (100) Ge p- and n-MOSFETs than the effective mobility from the split C-V method. It is confirmed that the discrepancy between the Hall and the effective mobility of Ge MOSFETs cannot be explained by the Hall factor under carrier scattering mechanisms known for MOSFETs. Thus, this discrepancy is attributed to the difference in N<sub>s</sub> between the Hall measurement and the split C-V (Fig. 2), which can be interpreted as the N<sub>s</sub> loss due to interface states near or

Fig. 2.  $N_s$  evaluated from  $C_{gc}$  and Hall measurements of Ge (100) p- and n-MOSFETs with different GeO<sub>x</sub> IL thicknesses.

inside VB and CB, as recently been observed in InGaAs MOS interfaces <sup>[7]</sup>.

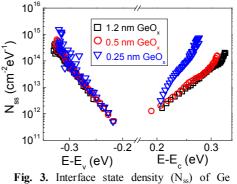

The existence of interface states inside the bands can lead to the rapid decrease of the effective mobility in high normal field of Ge MOSFETs. The energy distributions of the interface state density (N<sub>ss</sub>) can be evaluated from the difference in N<sub>s</sub> between the Hall measurement and the split C-V <sup>[7]</sup> for p- and n-MOSFETs under an assumption of the Hall factor of 1. It is found that large amounts of N<sub>ss</sub>,  $\sim 10^{14}$  cm<sup>-2</sup>eV<sup>-1</sup> around energies of E<sub>v</sub>-0.3 eV and E<sub>c</sub>+0.3 eV, exist inside VB and CB for the present Ge MOSFETs. Particularly, N<sub>ss</sub> inside CB is dependent on the GeO<sub>x</sub> thickness, leading to the strong GeO<sub>x</sub> thickness dependence of the electron mobility.

**Conclusion** The amount of  $N_{ss}$  inside the VB and CB of Ge has been evaluated through Hall measurement of Ge MOSFETs. It is confirmed that the carrier trapping due to  $N_{ss}$  is a dominant factor of the effective mobility reduction for Ge p- and n-MOSFETs in high  $N_s$  region.

Acknowledgement This work was supported by Grant-in-Aid for Scientific Research (No. 23246058) from MEXT of Japan.

References [1] S. Takagi et al., IEDM, 57 (2003). [2] Y. Nakakita et al., IEDM, 877 (2008). [3] K. Morii et al., IEDM, 681 (2009). [4] C. Lee et al., IEDM, 416 (2010). [5] R. Zhang et al., IEDM, 642 (2011). [6] R. Zhang et al., VLSI, 161 (2012). [7] N. Taoka et al., IEDM, 311 (2011).

Fig. 1. Effective and Hall mobility of Ge (100) pand n-MOSFETs with different  $GeO_x$  IL thicknesses.

Fig. 3. Interface state density ( $N_{ss}$ ) of Ge MOSFETs with different GeO<sub>x</sub> IL thicknesses.