## 極薄 GeO<sub>X</sub> 界面層を有する Y<sub>2</sub>O<sub>3</sub>/Ge ゲートスタックの低温形成 Low-temperature fabrication of Y<sub>2</sub>O<sub>3</sub>/Ge gate stacks with ultrathin GeO<sub>X</sub>-interlayer

九大・大学院総合理工学府<sup>1</sup>, 九大・産学連携センター<sup>2</sup>, 学振特別研究員<sup>3</sup> 永冨 雄太<sup>1</sup>, 小島 秀太<sup>1</sup>, 亀沢 翔<sup>1</sup>, 山本 圭介 <sup>2,3</sup>, 王 冬<sup>1</sup>, 中島 寛<sup>2</sup> I-Eggs, Kyushu Univ.<sup>1</sup>, KASTEC, Kyushu Univ.<sup>2</sup> JSPS Research Fellow <sup>3</sup>: Y. Nagatomi<sup>1</sup>, S. Kojima<sup>1</sup>, S. Kamezawa<sup>1</sup>, K. Yamamoto<sup>2,3</sup>, D. Wang<sup>1</sup>, H. Nakashima<sup>2</sup> E-mail: 2ES12029@s.kyushu-u.ac.jp

## 1. はじめに

近年、Si よりも高いキャリア移動度を有する Ge-MOSFET の研究開発が加速している。しかし、Ge は Si よりもドーパントの拡散係数が大きく固溶度が低いため、高濃度で浅い接合の S/D 形成は困難である。この問題を解決するため、我々はメタル S/D 型 MOSFET に着目している。既に、電子障壁の低い TiN コンタクト技術を確立し[1]、TiN を S/D に用いたメタル S/D 型の n-MOSFET 動作を実証している。 [2] この MOSFET をゲートラストプロセスで作製する場合、TiN-S/D 形成後のゲートスタックは 400℃ 以下で形成しなければならない。今回、high-k/Ge スタックに於いて界面欠陥が Y で終端されるとの報告がある  $Y_2O_3$  に着目し[3]、 $Y_2O_3$ /Ge ゲートスタックの低温形成を試みたので、その結果を報告する。

## 2. 試料作製

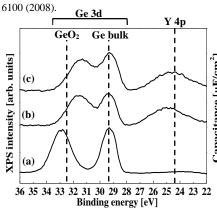

n-および p-形(100)Ge 基板の抵抗率はそれぞれ 0.29 および 0.38  $\Omega$ cm である。Ge 基板を化学洗浄後、犠牲酸化を行った。試料を PVD チャンバーに搬入し、真空アニールにより  $GeO_2$  を完全に揮発させ、表面クリーニングを行った。その後、同一真空中で低パワー( $P_{rf}=5$  W)の  $O_2$  添加 rf スパッタリング(ターゲット: $Y_2O_3$ )を室温で行った。この試料の XPS スペクトルを Fig. 1(a)に示す。パワーが低いため、 $Y_2O_3$  のスパッタリングは行われず、Ge 表面に  $GeO_X$  が形成されたことが分かる。次に、 $P_{rf}=20$  W とし、 $O_2$  添加無しで 3 nm- $Y_2O_3$  を室温で堆積した。この試料の XPS スペクトルを Fig. 1(b)に示す。 $GeO_X$  に対応する信号が低エネルギー側にシフトしていることから、 $Y_2O_3$  が  $GeO_X$  と反応し、 $YGeO_X$  が形成されたことが分かる。その後、同一チャンバー内で  $400^\circ$ C-30min の真空アニールを施した。この試料の XPS スペクトル[Fig. 1(c)]から、 $YGeO_X$  の組成に大きな変化がないことが分かる。最後にゲート電極として、TiN を堆積して 350°C-20min の PMA を行い、Al の堆積後に電極加工を行った。こうして Al(100 nm)/TiN(50 nm)/ $Y_2O_3$ / $YGeO_X$ / $GeO_X$

## 3. 電気特性

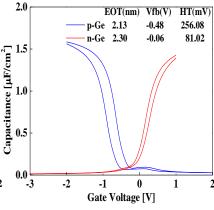

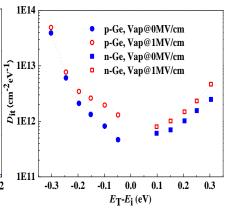

試作した MOSCAP の C-V 特性(周波数: 1MHz)を Fig. 2 に示す。n-および p-MOSCAP は典型的な MOS 特性を示した。この C-V 特性から得られた等価  $SiO_2$  換算膜厚(EOT)、フラットバンド電圧( $V_{fb}$ )、 ヒステリシス(HT)を Fig. 2 中に示す。一定温度 DLTS で得られた界面準位密度( $D_{it}$ )のエネルギー分布を Fig. 3 に示す。図中には、1 MV/cm のストレス電界印加の結果も示す。禁制帯中央付近で  $5x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>、価電子帯近傍で  $3x10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup>、伝導帯近傍で  $2x10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>であった。伝導帯側で低い  $D_{it}$  を示すことに加えてスロートラップも少ないことから、n-MOSFET のゲートとして有望である。 [参考論文] [1] K. Yamamoto et al., JJAP 51, 070208 (2011), [2] K. Yamamoto et al., APEX 4, 051301 (2011), [3] K. Kita et al., Appl. Surf. Sci. 254,

Fig. 1. XPS spectra of samples with (a)  $O_2$  irradiation, (b)  $Y_2O_3$  sputtering, and (c) annealing at  $400^{\circ}$ C.

Fig. 2. C-V characteristics at 1 MHz for n- and p-MOSCAPs with TiN/Y<sub>2</sub>O<sub>3</sub>/YGeO<sub>X</sub>/GeO<sub>X</sub>/Ge structures.

Fig. 3.  $D_{it}$  distributions for n- and p-MOSCAPs with TiN/Y<sub>2</sub>O<sub>3</sub>/YGeO<sub>x</sub>/GeO<sub>x</sub> structures