## 基板バイアスと PD/FD 遷移を用いた 良好なサブスレッショルド係数を有する SOI MOSFET

SOI MOSFET with Good Subthreshold Slope

Using Substrate Bias and PD/FD Transition

東大生研

○黒崎 洋、平本 俊郎

IIS, University of Tokyo, You Kurosaki and Toshiro Hiramoto E-mail: kurosaki@nano.iis.u-tokyo.ac.jp

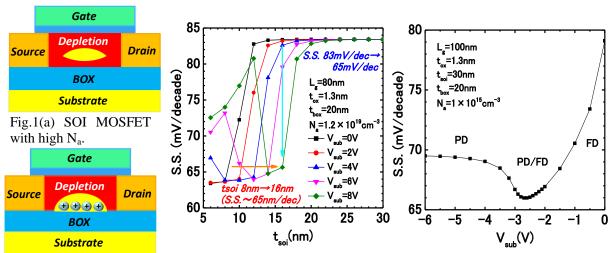

【はじめに】 増大する VLSI の消費電力を抑制するためには、MOSFET のサブスレショルド係数(S)を小さ くする必要がある。 完全空乏型(FD) SOI MOSFET は良好な S を有するデバイスである。 ところが、 短チャ ネル効果を抑えて良好な S を得るには、SOI 膜厚(tsoi)をゲート長(Le)の 1/4 程度まで薄くしなければなら ず、オン電流の劣化や量子ゆらぎによるしきい値電圧の不安定性といった問題を抱えている. 本研究で は、基板バイアスを用い、より厚い tsoiでも良好な S を示す MOSFET を提案する.【原理】まず、高濃度 SOI を有する SOI MOSFET (Fig.1(a))で原理を説明する. V<sub>ss</sub>=0V で t<sub>soi</sub> が空乏層厚よりわずかに厚い(部 分空乏(PD))と、ボディ電位が固定されていればオフ電流( $I_{off}$ )は抑制されるが PD なので  $V_{es}$ =0V 付近で はSは悪い.  $V_{gs}$ を加えると空乏層が埋込酸化膜(BOX)に達し,  $PD \rightarrow FD$  に遷移するため, S が改善する. このように PD/FD 遷移が起こると  $I_{off}$ を抑えつつ良好な S が得られる. 正の基板バイアス( $V_{sub}$ )を印加する と、BOX 直上にも空乏層が生じ、さらに厚い t<sub>soi</sub> でも PD/FD 遷移が起こる. Fig.2 に L<sub>g</sub>=80nm の SOI MOSFET における S と  $t_{soi}$  の関係のデバイスシミュレーション結果を示す.  $V_{sub}$  が大きいほど厚い  $t_{soi}$  でも 60mV/dec に近い S が得られており、V<sub>sub</sub>=8V では良好な S が得られる t<sub>soi</sub>を 8nm から 16nm へ厚くする ことができている. しかし, この例では高濃度 SOI チャネルが必要であり, ばらつきの観点から実用的では ない. 【提案デバイス】 そこで、Fig.1(b)のデバイスを提案する. SOI チャネルはイントリンジックである. 負 の  $V_{sub}$  を印加し SOI/BOX 界面に正孔を蓄積させ、 $V_{ss}$ =0V で PD 状態とする.  $V_{ss}$ を加えると正孔が消え FD 状態となり、PD/FD 遷移が生じる. Fig.3 に  $L_g$ =100nm、 $t_{soi}$ =30nm における S と  $V_{sub}$ の関係のシミュレ ーション結果を示す.  $V_{sub}$ =0V では正孔蓄積が起こらず  $V_{gs}$ の全範囲で FD 状態となり, S は 80mV/dec 程度と悪い. 一方、 $V_{sub}$ =-2.5V 付近では、PD/FD 遷移が見られ、S が極小となっている. S は 66mV/dec と小さい. さらに  $V_{sub}$  を印加すると  $V_{gs}$  の全範囲で PD 状態となり, S は劣化する. 【結論】 基板バイアス印 加よる正孔蓄積とPD/FD遷移により、厚いt<sub>soi</sub>でも良好なSが得られることを示した.

Fig.1(b) SOI MOSFET with intrinsic channel. Holes are accumulated at SOI/BOX interface.

Fig.2 Simulated S vs.  $t_{soi}$  in SOI MOSFET with high  $N_a$ .

Fig.3 Simulated S vs. V<sub>sub</sub> in SOI MOSFET with intrinsic channel.