## サラウンドゲーティングナノポアデバイスによる DNA 検出

Detection of DNA using Surround Gating Nanopore Devices 阪大産研 <sup>°</sup>龍崎奏,筒井真楠,大城敬人,古橋匡幸,横田一道,谷口正輝,川合知二 ISIR Osaka Univ., <sup>°</sup>Sou Ryuzaki, Makusu Tsutsui, Takahito Ohshiro, Masayuki Furuhashi, Kazumichi Yokota, Masateru Taniguchi, and Tomoji Kawai

E-mail: ryuzaki@sanken.osaka-u.ac.jp

【はじめに】個別可医療の実現に向け、ヒトゲノムを高速・低コスト(1日・10万円程度)で解読する DNA シークエンサー(塩基識別)の開発が必要不可欠とされている。本研究室では、直径  $1\sim2\,$  nm 程度のポアにナノギャップ電極を組み込み、一本鎖 DNA がナノポアを通過する際に生じるナノギャップ電極間のトンネル電流変化から塩基識別を行う手法を考案している(図  $1)^{[1]}$ 。しかしながら、ナノポアを通過する DNA が高速であるため、トンネル電流測定がその速度に追従できず、トンネル電流変化には複数の塩基情報が反映されてしまう。本研究室では DNA の速度制御法として、ナノポアの側壁を負に帯電させることで、ナノポア内部に DNA の移動方向とは逆向きの電気浸透流を発生させ、DNA の速度を減少させられることを理論的に明らかにしてきた[2]。

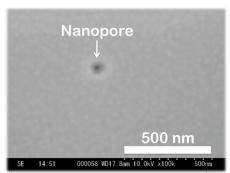

本研究では、ナノポアの側壁を帯電させるために金属電極(Pt/Au/Pt)でナノポアを覆った、サラウンドゲート電極を有するナノポアを作製し(図 2)、ナノポアを通過する DNA の速度とゲート電圧 ( $V_g$ ) の相関性を調べることで、理論的に予測されているサラウンドゲーティングナノポアデバイス特性の評価を行った。

【実験方法】電子線描画により  $Si_3Ni_4$ 基板上に直径 100 nm、厚さ 35 nm のナノポアを作製した後、スパッタ法によりナノポアを覆うようにゲート電極(Pt(2 nm)/Au(70 nm)/Pt(2 nm))を蒸着した。ナノポアの最終的な径は走査型電子顕微鏡(SEM)により確認をした。

流路がパターニングされた PDMS でナノポアの上下を封止し、KCI に分散させた DNA を流路に流した。電気泳動によって DNA はポアを通過し、その際にポアに流れるイオン電流が減少するため、そのイオン電流減少時間から DNA の速度を見積もった。

【結果】本実験では、サラウンドゲート電極にゲート電圧を  $V_g$  = -500 mV かけることで、ナノポアを通過する DNA の速度が  $V_g$  = 0 mV 時と比べおよそ 1/10 まで減少した。これは、サラウンドゲート電極(ポア側壁)を負に帯電させたことで、DNA の移動方向とは逆向きの電気浸透流がポア内部に生じたためであると考えられる。電気浸透流の強度は、KCI の濃度や電気泳動の電場強度に依存するため、条件を最適化することで、DNA シークエンスが可能な速度まで減速させられることが示唆された。

- [1] M. Tsutsui, et al., Nature Nanotechnol. 5, 286 (2010).

- [2] Y. He, et al., ACS Nano 5, 5509 (2011).

図1. ゲーティングナノポアを用いた DNA シークエンサー

図2. サラウンドゲーティング ナノポア