## SrSiO<sub>x</sub>/Si 構造の熱安定性と電気特性の評価

Thermal stabitly and electrical characterization of SrSiOx/Si structure 兵庫県立大学 <sup>1</sup>,明治大学 <sup>2</sup>,JST-CREST <sup>3</sup> <sup>0</sup>谷脇 将太 <sup>1</sup>,豊島 祐樹 <sup>1</sup>,堀田 育志 <sup>1,3</sup>, 吉田 晴彦 <sup>1,3</sup>,新船 幸二 <sup>1,3</sup>,小椋 厚志 <sup>2,3</sup>,佐藤 真一 <sup>1,3</sup>

Univ. of Hyogo<sup>1</sup>, Meiji Univ.<sup>2</sup>, JST-CREST<sup>3</sup> Shota Taniwaki<sup>1</sup>, Yuki Toyoshima<sup>1</sup>,

Yasushi Hotta<sup>1,3</sup>, Haruhiko Yoshida<sup>1,3</sup>, Koji Arafune<sup>1,3</sup>, Atsushi Ogura<sup>1,2</sup>, and Shin-ichi Satoh<sup>1,3</sup>

E-mail: eo09f069@steng.u-hyogo.ac.jp

【はじめに】厚さが  $100 \mu$  m を切る薄型の結晶シリコン太陽電池セルの開発では、界面でのキャリアの表面再結合による効率の低下が顕著になるため、その表面再結合速度を低減させるパッシベーション技術が一層重要になる。前回  $^{1)}$ 、我々は新規の電界効果パッシベーション層の候補材料としてストロンチウムシリケイト( $SrSiO_x$ ) を提案し、その固定電荷に関する報告を行った。 $SrSiO_x$  は、Si 基板との間に  $SiO_x$  が形成されないことから、単純な構造で良好な界面特性が得られることが期待できる。一方で、 $SrSiO_x$  層自体の電気特性は、膜中の酸素欠損に大きく依存するため、これを効果的に消滅させるアニール処理が必要になることが分かってきた。今回の講演会では、 $SrSiO_x$ /Si 構造の熱安定性の評価を通じてアニール条件の最適化を行い、電気特性の改善を試みたので報告する。

【実験方法】 $SrSiO_x$ 層は、パルスレーザー堆積法によって SrO を p-Si(100)基板上に成膜し、それをポストアニール処理によってシリケイト化することによって作製した。SrO の成膜は超高真空チャンバー中(<  $10^{-6}$  Pa)において室温で行い、その後 1atm の酸素雰囲気中において温度 500  $\mathbb{C}$

~800 $^{\circ}$ C、時間 0min~960min o条件でポストアニール処理を行った。X線光電子分光(XPS)を用いて、得られた  $SrSiO_x$ 層の構造を評価した。また、 $Au/SrSiO_x(50ML)/p-Si(100)$ 構造の試料について容量一電圧(C-V)測定を行った。

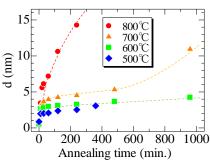

【実験結果】図 1(a)には今回用いた試料構造の模式図を、(b)には Si 2p 領域の内殻光電子スペクトルの上部層 Si ピークと基板 Si ピークの比より決定した上層部の厚さ d をアニール時間の関数でプロットしたものを示す。図 1(b)より、800℃ではアニール直後から膜厚が急激に増加しており、また 700℃でも 600 分以上のアニールで膜厚の増加が見られた。一方、600℃以下では、長時間のアニールに対しても膜厚が一定の厚さに収まっている。これらの膜厚増加の原因は、界面に SiO2 層が成長しているためであり、よって SrSiO $_{x}$ /Si 構造は 600℃以下で安定に保持されることが分かった。C-V 測定の結果では、温度:600℃、時間:120分以上において、蓄積側のリークがない良好な C-V 特性が得られ、なお且つ負のフラットバンドシフトが得られた。

図 1.(a)本実験の試料構造模式図。(b)各 アニール温度における上部層の膜厚の アニール時間依存性。

【参考文献】1) 堀田育志 et al. 第 73 回応用物理学会学術講演会 講演予稿集 13p-PB12-1(2012)