# C-Axis Aligned Crystalline In-Ga-Zn-Oxide Flip Flop を実装した 低消費電力 8bit プロセッサ

A Low-Power 8bit Processor with C-axis Aligned Crystalline In-Ga-Zn-Oxide Flip Flops

(株)半導体エネルギー研究所 ○前田 修平, 小林 英智, 大嶋 和晃, 米田 誠一, 西島 辰司,

王丸 拓郎, 戸松 浩之, 古谷 一馬, 石山 貴久, 附田 一起, 熱海 知昭, 塩野入 豊,

加藤 清, 前橋 幸男, 小山 潤, 山﨑 舜平

Semiconductor Energy Laboratory Co., Ltd., OS. Maeda, H. Kobayashi, K. Ohshima, S. Yoneda, T. Nishijima, T. Ohmaru, H. Tomatsu, K. Furutani, T. Ishiyama, K. Tsukida, T. Atsumi, Y. Shionoiri, K. Kato, Y. Maehashi, J. Koyama, S. Yamazaki

E-mail: sm1179@sel.co.jp

### 【はじめに】

低消費電力化を目指したノーマリオフコンピューティング技術が注目されている[1]。ノーマリオフ動作を実現するためには不揮発性メモリにデータを保持する必要があり、通常動作に加えて時間的・電力的なオーバーヘッドが発生する。より細粒度の動作を実現するためには、これらのオーバーヘッドを削減する必要がある。また、ノーマリオフ動作による電力削減効果はBreak even time (BET)によって示される。

一方で、我々は C-Axis Aligned Crystalline In-Ga-Zn-Oxide FET(CAAC-IGZO FET)のオフ電流がゲート幅 1µm あたり 100yA (85℃)程度であることを発見し[2]、Si-FET と組み合わせ、不揮発性メモリへ応用[3]し、不揮発性フリップフロップ(FF)を実装したプロセッサの試作[4]を行なってきた。

今回、我々は CAAC-IGZO FF 構造を改良し、オーバーヘッドの削減を図った。さらに電源コントローラや電源制御スイッチを実装し、1チップ内でノーマリオフ駆動が可能なプロセッサを試作した。本報告では以上のノーマリオフプロセッサに関して報告する。

#### 【データ保持型 FF】

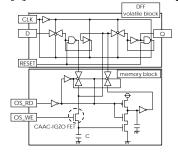

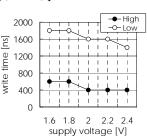

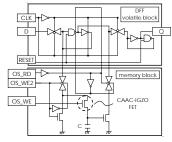

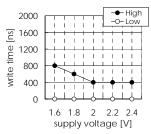

図1に示す様に、CAAC-IGZO FF は標準的な DFF を含む揮発性部と CAAC-IGZO FET と保持容量(C=1pF)を含むメモリ部によって構成される。データの退避および復帰時のみメモリ部へアクセスする。以前の FF では 2.0V におけるデータの書込み時間は1600ns である(図1)のに対し、本報告の FF はメモリ部に改良を加えた結果、400ns となり(図 2)、書込み時間を1/4 に短縮することができた。また、室温において、書換え回数 10<sup>11</sup> 回後でも書込み時間はほとんど変化しないことを確認している。

## 【ノーマリオフプロセッサの動作】

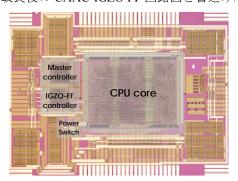

図 3 に本報告のノーマリオフプロセッサの 外観図を示す。ノーマリオフ動作によって音楽 再生プログラムを実行した際の BET は 2.0V、 25MHz において 25.3µs となった。電源オフ時 間が数十 μs 以上のアプリケーションにおいて、 本プロセッサは電力削減効果が見込めること を示唆している。

#### 【参考文献】

[1]K. Ando: FED Review, 1 (2001) 1.

[2]K. Kato et al.: JJAP, **51** (2012) 021201.

[3]H. Inoue et al.: IEEE JSSC, 47 (2012) 2258.

[4]S. Yamazaki: SID 2012 Dig., 2012, p.183.

図 1.以前の CAAC-IGZO FF 回路図と書込み時間

図 2.改良後の CAAC-IGZO FF 回路図と書込み時間

図3:ノーマリオフプロセッサの外観図