## 有機薄膜トランジスタの閾値電圧制御:集積回路応用に向けて

Threshold voltage control in organic thin-film transistors toward their application to integrated circuits

神戸大院工<sup>1</sup>, 東大ナノ量子機構<sup>2</sup>, 東大生研<sup>3</sup> <sup>°</sup>木村 由斉<sup>1</sup>, 北村 雅季<sup>1,2</sup>, 荒川 泰彦<sup>2,3</sup>

Kobe Univ.<sup>1</sup>, NanoQuine, Univ. Tokyo<sup>2</sup>, and IIS, Univ. Tokyo<sup>3</sup>

\*Yoshinari Kimura<sup>1</sup>, Masatoshi Kitamura<sup>1,2</sup>, and Yasuhiko Arakawa<sup>2,3</sup>

E-mail:135t222t@stu.kobe-u.ac.jp

有機薄膜トランジスタ(TFT)を実用的な回路に応用する場合には閾値電圧の制御が求められる. 我々は熱酸化膜表面に対する酸素プラズマ処理により,有機トランジスタの閾値電圧を制御することに成功した[1,2]. 一方,集積回路へ応用する場合,製膜した絶縁膜に対して有効な閾値電圧制御の方法が必要である. 本研究では,スパッタリング製膜した  $SiO_2$  絶縁膜に酸素プラズマ処理を行ったペンタセン TFT を作製し,その評価を行ったのでそれについて報告する.

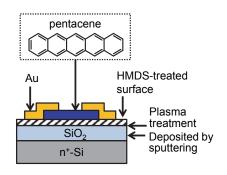

図 1 に作製したペンタセン TFT の断面図を示す. ゲート電極として機能する  $n^+$ -Si 基板上に, 絶縁膜として  $SiO_2$  (ゲート容量 16  $nF/cm^2$ ) をスパッタリングにより製膜した.  $SiO_2$  表面は酸素プラズマにより処理を行った. 閾値電圧との関係を調べるため,処理時間を 30, 60, 120 s とした. プラズマ処理後,HMDS 膜を形成し,その上に,チャネル層のペンタセン,ソース・ドレイン電極の金をそれぞれ真空蒸着により製膜した.

図 2 はチャネル長 60  $\mu$ m のペンタセン TFT のドレイン電流( $I_D$ ) - ゲート電圧( $V_G$ )特性と, $I_D$ - $V_G$  特性より算出した TFT の閾値電圧である.同様に  $I_D$ - $V_G$  特性より移動度を算出したところ,プラズマ処理を行わなかった TFT は,プラズマ処理した TFT に比べ低い移動度を示した.これは HMDS 膜の形成が不十分であったためと考えられる. 閾値電圧については,プラズマ処理を行った TFT では,プラズマ処理時間の増加と共に正方向に変化している. 結果として,熱酸化膜と同様にスパッタリング製膜した絶縁膜に対しても,酸素プラズマ処理による閾値電圧制御が有効であることが分かった.以上より,この作製プロセスによる閾値電圧制御の集積回路への応用が期待できる.

(a) 0.4 Drain current  $|I_{D}|^{1/2}$  (10<sup>-3</sup> A<sup>1/2</sup>) 3 ><sup>€</sup> 0 **Threshold Voltage** Plasma time -2 0,30,60,120 s -3 20 40 60 80 100 120 -20 -15 -10 -5 0 treatment time t\_ (s) Gate voltage  $V_{G}(V)$

Fig.1. Schematic for a pentacene TFT with SiO<sub>2</sub> deposited by sputtering.

Fig.2. (a) Transfer characteristics and (b) threshold voltages of pentacene TFTs with different plasma-treatment time.

【謝辞】本研究は文部科学省イノベーションシステム整備事業および科研費基盤研究(C) (24550211)の支援により遂行された.

【参考文献】[1] Y. Kimura, et al., ISCS 2013, MoPC-09-04. [2] 木村 他, 2014 年第 61 回応用物理学会春季学術講演会, 17p-E3-4