## エピタキシャルリフトオフ(ELO)法による 大口径薄膜 Ge-on-Insulator 基板 Large-scale Ultrathin Ge-on-Insulator wafer Using Epitaxial Lift-Off (ELO) Technique

產総研<sup>1</sup>、住友化学<sup>2</sup>、日立国際電気<sup>3</sup> <sup>0</sup>前田辰郎<sup>1</sup>、三枝栄子<sup>1</sup>、石井裕之<sup>1</sup>、服部浩之<sup>1</sup>、 板谷太郎<sup>1</sup>、安田哲二<sup>1</sup>、前田敦彦<sup>1</sup>、倉島優一<sup>1</sup>、高木秀樹<sup>1</sup>、 青木健志<sup>2</sup>、山本武継<sup>2</sup>、市川磨<sup>2</sup>、長田剛規<sup>2</sup>、高田朋幸<sup>2</sup>、秦雅彦<sup>2</sup>、 由上二郎<sup>3</sup>、小川有人<sup>3</sup>、菊池俊之<sup>3</sup>、国井泰夫<sup>3</sup>

AIST<sup>1</sup>, Sumitomo Chemical Co., Ltd.<sup>2</sup>, and Hitachi Kokusai Electric Inc.<sup>3</sup>

°T. Maeda<sup>1</sup>, E. Mieda<sup>1</sup>, H. Ishii<sup>1</sup>, H. Hattori<sup>1</sup>, T. Yasuda<sup>1</sup>, A. Maeda<sup>1</sup>,

Y. Kurashima<sup>1</sup>, H. Takagi<sup>1</sup>, T. Aoki<sup>2</sup>, T. Yamamoto<sup>2</sup>, O. Ichikawa<sup>2</sup>, T. Osada<sup>2</sup>, T. Takada<sup>2</sup>, M. Hata<sup>2</sup>, J. Yugami<sup>3</sup>, A. Ogawa<sup>3</sup>, T. Kikuchi<sup>3</sup>, Y. Kunii<sup>3</sup>

E-mail: t-maeda@aist.go.jp

## 【背景・目的】

LSI の微細化が物理的限界に近づく中、更なる高性能化を図るために、キャリア移動度の高い Ge チャネルへの期待が高まっている。これまでに、Ge 特有の高品質なゲートスタック技術の開発と高移動度実証により、チャネル材料としては有用性が示されてきた。しかしながら、高度集積化には、Ge on Si や Ge-on-Insulator などの基板エンジニアリングが鍵となる。そこで我々は、低温貼り合せ技術とエピタキシャルリフトオフ(ELO)法を用いた高品質 Ge 層の転写技術を開発してきた $^{[1]}$ 。今回、量産を見据えた大口径高品質薄膜 (GeOI)基板を作製したので報告する。

## 【結果と考察】

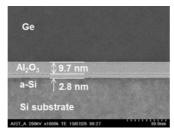

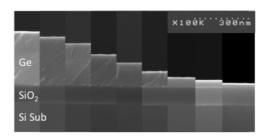

ELO 法は、剥離層の横方向エッチングを利用するため、大面積での全面転写には適さない。しかし ながら、実際のデバイス用途では、Si ウエハー全面に Ge 層が必要ではなく、チャネルを形成する領域 にのみあれば良い。本研究では、必要とする材料を任意の場所に転写できるパターン ELO 法を採用し た。まず、4"-GaAs 基板上に剥離層となる AlAs 層を挟んで高品質な Ge 層をエピタキシャル成長させ、 Ge/AlAs/GaAs ドナーウエハーを準備する。その後、埋め込み絶縁層および Ge 層のパッシベーション 膜として機能する Al<sub>2</sub>O<sub>3</sub> 膜を堆積させた。Ge/AlAs 層を L/S パターンや格子パターンなど任意の構造に エッチング後、ハンドル Si ウエハーと接合した。熱膨張係数差のある異種材料同士の接合では、高温 プロセスで接合界面剥離の可能性があることから、我々は、Ar ビームによる表面活性化を利用した常 温接合、またはウエットプロセスによる接合法を用いた。接合後、AlAs 剥離層を HCI 水溶液により溶 解し、GaAs 基板を剥離、Epi-Ge 層を 4"-Si ウエハー上へ転写した (Fig. 1)。断面 TEM 像から、接合界 面は欠陥なく非常に平坦な界面を形成していることがわかる(Fig. 2)。スマートカット法と比べると、 接合と剥離プロセスすべて低温で行っており、イオン注入など転写された Ge 層へのプロセスダメージ が少ないことも本手法の利点である。Fig. 3 は、転写後 Ge 層を 300nm から 18nm まで薄膜化した GeOI 基板の断面 SEM 像である。10nm 以下の超極薄 GeOI 基板の作成も可能である。さらに、300 mm ウエ ハーなど大口径化技術として、一枚の基板に複数枚貼り合わせるマルチ転写も実証している。今回の 開発した ELO-GeOI 技術は、高性能 Ge LSI に向けた実用的な基板エンジニアリングとして期待される。

[1] T. Maeda et al., Microelectron. Eng., 109 (2013) 133.

Fig. 1 Photograph of 4" patterned GeOI wafer.

Fig. 2 XTEM image of GeOI wafer .

Fig. 3 XSEM images of GeOI wafers with the different thicknesses from 300nm down to 18nm.