## DLTS 法による窒化後酸化 SiC-MOSFET の界面準位評価

**DLTS Study of SiC-MOSFET Interface Traps Following Oxidation After Nitridation** 東京工業大学<sup>1</sup>,三菱電機先端総研<sup>2</sup> ○ 長谷川淳一<sup>1</sup>,須藤建瑠<sup>1</sup>,岩崎孝之<sup>1</sup>,小寺哲夫<sup>1</sup>,

古橋壮之 $^2$ ,野口宗隆 $^2$ ,中田修平 $^2$ ,西村 正 $^1$ ,波多野睦子 $^1$

Tokyo Institute of Technology<sup>1</sup>, Mitsubishi Electric Corp. Advanced Technology R&D Center.<sup>2</sup>

<sup>O</sup>Junichi Hasegawa<sup>1</sup>, Takeru Suto<sup>1</sup>, Takayuki Iwasaki<sup>1</sup>, Tetsuo Kodera<sup>1</sup>, Masayuki Furuhashi<sup>2</sup>,

Munetaka Noguchi<sup>2</sup>, Shuhei Nakata<sup>2</sup>, Tadashi Nishimura<sup>1</sup>, Mutsuko Hatano<sup>1</sup>

E-mail: hasegawa.j.ad@m.titech.ac.jp

SiC-MOSFET のしきい値電圧  $V_{th}$  は、雑音等による誤点狐を防ぐため大きくする必要がある。従来のチャネル濃度による  $V_{th}$  制御では移動度が低下するという問題があったが、ゲート酸化膜の窒化後にウェット酸化を行うことにより、移動度の低下を回避して  $V_{th}$  を正にシフトできる事が分かった  $^{[1]}$ 。本研究では、酸化膜形成後の窒化および窒化後のウェット酸化が SiC-MOSFET の界面準位に与える影響を、浅い準位から深い準位まで精度良く測定できる DLTS(Deep Level Transient Spectroscopy) 法によって調べた。

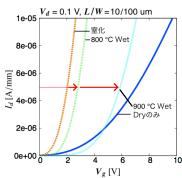

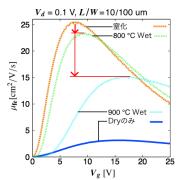

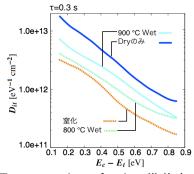

Si 面 n チャネル 4H-SiC  $MOSFET(L/W=10/100 \mu m)$  において、高温ドライ酸化によるゲート酸 化膜形成、酸化膜形成後の NO アニールによる窒化、窒化後の 800, 900 °C ウェット酸化を行った 4 サンプルを評価した。図1 に $I_dV_g$  特性を、図2 に $V_g$  に対する電界効果移動度 $\mu_{fe}$  の変化を示す  $(V_d=0.1 \text{ V})$ 。 窒化によって S 値は 0.3 倍、 $\mu_{fe}$  は 8.7 倍に向上した。 窒化後の 800 °C ウェット酸化に より、S 値と $\mu_{fe}$  の低下を抑制しつつ  $V_{th}$  を正に  $0.75~\rm V$  シフトさせることができた。 $900~\rm ^{\circ}C$  ウェッ ト酸化では窒化後に比べ  $V_{th}$  は正に 4.0 V シフトした一方、S 値は 1.5 倍、 $\mu_{fe}$  は 0.65 倍に低下した。 図 3 に FET と同じ条件で作製した n 型キャパシタを用いて時定数  $\tau$ =0.3 s の DLTS 信号を測定 し、界面準位密度  $D_{it}$  を算出した結果を示す。逆バイアスは空乏層幅が約  $300~\mathrm{nm}$  になる電圧とし、 パルス印加時のバイアスはフラットバンド電圧  $V_{fb}$  より+2 V 酸化膜側に印加した。エネルギーレ ベルは測定温度から、 $D_{it}$  は  $1/C(t)^2$  の時間微分から算出した。図 3 より、 $D_{it}$  は窒化によって約 0.25 倍に低減している。窒化によって移動度と S 値が向上する要因と考えられる。窒化後の 800  $^{\circ}$ C ウェット酸化では、窒化サンプルと比較して  $D_{it}$  は増加しているが、 $0.3~\mathrm{eV}$  を境に浅い準位と深 い準位で増加の程度に違いが見られる。移動度が低下せず V,,, が正シフトする一因であると考えら れるが、定量的な検討も含めて今後明らかにしていく。900°Cウェット酸化では、窒化サンプル と比較して、浅い準位も含め準位密度が約2倍に増加する。この結果も図1、図2に示した特性と 対応する。

図 1: MOSFET の  $I_dV_g$  特性

図 2: MOSFET の移動度

図 3: MOS キャパシタの準位密度

[1] M. Furuhashi, et.al: Proceedings of The 25th ISPSD, Kanazawa (2013) 2-4.