## Al<sub>2</sub>O<sub>3</sub> をゲート絶縁膜とした歪み Ge MOS 構造の電気特性 Electrical properties of strained Ge MOS structure with Al<sub>2</sub>O<sub>3</sub> gate dielectric

都市大総研<sup>1</sup>,慶應義塾大<sup>2</sup>,Warwick 大<sup>3</sup>

○ 深山 剛 <sup>1</sup>, 田中 伸之介 <sup>2</sup>, 田中 貴久 <sup>2</sup>, マクシム ミロノフ <sup>3</sup>,

牧 英之2, 伊藤 公平2, 澤野 憲太郎1

Tokyo City Univ. 1, Keio Univ. 2, Univ. of Warwick 3

° T. Fukayama<sup>1</sup>, S. Tanaka<sup>2</sup>, T. Tanaka<sup>2</sup>, M. Myronov<sup>3</sup>, H. Maki<sup>2</sup>, K. M. Itoh<sup>2</sup>, and K. Sawano<sup>1</sup> E-mail: sawano@tcu.ac.jp

【はじめに】 歪み Ge は、次世代 CMOS の p チャネル材料として期待されており、 $3000cm^2/Vs$  を超える室温正孔移動度[1]も報告されている。さらに Ge はスピン軌道相互作用が大きいことから、高移動度 2 次元ホールガスによるスピンデバイス応用も検討されている。これらの実現に向けて最重要な課題は、良質な歪み Ge MOS 構造の形成といえる。今回我々は、ALD 法を用いて堆積した  $Al_2O_3$  をゲート酸化膜として用いた歪み Ge MOS 構造を作製し、電気特性評価を行った。

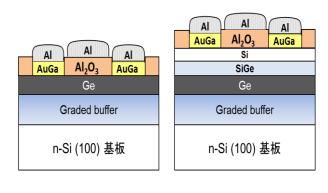

【実験】作製した試料構造を Fig.1 に示す。まず、n型 Si(100)基板上に RPCVD を用いて傾斜組成法により緩和 Si $_{0.6}$ Ge $_{0.4}$ バッファー層を作製した。 CMP による平坦化後、固体ソース MBE を用いて歪み Ge チャネル層  $10\,\mathrm{nm} \sim 20\,\mathrm{nm}$  を  $300\,^{\circ}$ Cで作製した。その上に Si/SiGe( $3\,\mathrm{nm}/20\,\mathrm{nm}$ )キャップ層の挿入するものとしないものを用意し、その上に ALD 法を用いてゲート酸化膜として  $\mathrm{Al}_2\mathrm{O}_3$  を堆積した。その後、試料上にホールバー、ゲート電極を形成し、ゲート付きホール測定を行った。

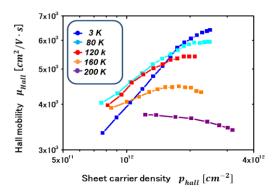

【結果】Fig.2 に歪み  $Ge\ 20\ nm$ 、キャップ層ありの試料について各温度ごとの正孔移動度の正孔密度依存性を示す。ゲートバイアスによって大きく正孔濃度を変調できていることが分かる。 $3\sim 160\ K$  では正孔密度が減少していくにつれて移動度も減少していることから、この温度領域では、主な散乱要因がイオン化不純物散乱であると考えられる。ここで特徴的なことは、 $3\ K$  の移動度が  $80\sim 160\ K$  よりも大幅に減少していくことである。これは、以前ゲート酸化膜として CVD で堆積した  $SiO_2$  を用いて調べた結果[2]とは異なる現象であり、現在その要因について検討中である。 $Ge\ Fr$  ネルへ直接  $Al_2O_3$  を堆積した構造については当日報告する。

【謝辞】本研究の一部は、文科省私立大学戦略的研究基盤形成支援事業、科学研究費補助金、総務省 SCOPE プロジェクトの支援を受けて行われた。

[1] T. Tanaka et al. APL 100, 222102 (2012). [2] K. Sawano et al. APEX 1, 011401 (2008).

Fig.1 歪み Ge MOS 構造

Fig.2 移動度の正孔密度依存性