# プログラマブルジョセフソン電圧標準用素子チップの伝熱解析

# Heat Transfer Analysis of a Programmable Josephson Voltage Standard Chip

#### 1. はじめに

現行の直流電圧の国家標準は、ジョセフソン効果を用いて 実現されている。従来のジョセフソン電圧標準 (CJVS) シス テムは素子チップを冷却するために継続的に液体へリウムを 使用する必要があり、維持や供給の安定性、コストが課題と なっていた。産総研では、液体へリウムを使用せずにチップ を冷却する機械式冷凍機を使ったプログラマブルジョセフソ ン電圧標準 (PJVS) システムの開発を進めている [1,2]。 本 研究では、機械式冷凍機を用いた場合に重要となる素子チッ プの発熱による影響や、表面温度の面内分布について計算機 シミュレーションにより解析した。

#### 2. PJVS 用素子チップと計算モデル

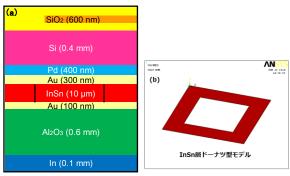

PJVS 用の素子チップは  $15 \text{ mm} \times 15 \text{ mm}$  の大きさの Si 基板上に形成された 524 288 個の NbN 系接合から成る[3]。一定温度に保たれたコールドステージにチップは置かれ、液体へリウムではなく機械式冷凍機で 10 K 前後に冷却される。今回のシミュレーションでは、層間絶縁の  $SiO_2$  層や素子実装のための InSn はんだ層などを考慮し、以下の 8 層からなるモデルを用いた(Fig. 1 (a))。最下層のコールドステージから①In (0.1 mm)、②Al $_2O_3$  (0.6 mm)、③Au (100 nm)、④InSn ( $10 \text{ }\mu\text{m}$ )、⑤Au (300 nm)、⑥Pd (400 nm)、⑦Si (0.4 mm)、⑧SiO $_2$  (600 nm)である。開発中の PJVS システムの電圧生成実験において、このチップは出力電圧が増加すると発熱が起こり、動作マージンに影響を及ぼすことが分かった[1]。また、素子の断面観察からInSn はんだ層に空乏がある可能性が分かったため、不均一性を模擬したシミュレーションも行った(Fig. 1 (b))。

Fig. 1 (a) Model for heat transfer analysis and (b) nonuniform InSn layer.

## 3. チップの発熱を考慮した伝熱解析

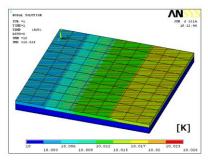

素子チップの発熱による温度分布を求めるため、有限要素法を用いた解析ソフト ANSYS® を使用し解析を行った。まず実装チップを最も単純にしたモデルを作成し伝熱解析をした。発熱部分はジョセフソン接合のある第 8 層目の  $SiO_2$  右側から 10 分の 7 の範囲(10.5 mm 幅)における 300 nm  $\sim 400$  nm の高さを発熱エリアと指定し(Fig.~1 (a))、発熱量は 10 V の出力に対応した 0.3 W とした。また In 層の下面の温度を 10 K とした。解析した結果を Fig.~2 に示す。

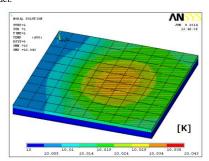

次に、実際の素子の断面観察で見られた InSn はんだ層の不均一性を考慮するため、InSn 層をドーナツ型にしたモデルを作製した。この解析用モデルでは、 $15\,\mathrm{mm}\times15\,\mathrm{mm}$  の層から中心  $9\,\mathrm{mm}\times9\,\mathrm{mm}$  の部分を抜き、上下の Au 層(③,⑤)と接触していない  $9\,\mathrm{mm}\times9\,\mathrm{mm}$  の範囲は真空とした(Fig.  $1\,\mathrm{(b)}$ )。他の与える条件は Fig.  $2\,\mathrm{o}$  のモデルと同様に設定し、解析した結果を Fig.  $3\,\mathrm{c}$  に示す。

Fig. 2 Temperature distribution on the chip-surface calculated based on a uniform model

Fig. 3 Temperature distribution on the chip-surface calculated based on a model with nonuniform InSn layer.

### 4. 考察とまとめ

全ての層を一様な面としたモデルの解析結果(Fig. 2)では、チップ中心と端の温度差は約0.02 K以下で、ほぼ均一な表面温度分布が得られた。一方 InSn 層の中心を抜いてより現実のチップに近づけた解析結果(Fig. 3)では、はんだ層の不均一性を反映した同心円状の温度分布が見られた。また、チップ内最高温度は10.04 Kとなり、均一な場合の約2倍の温度上昇が生じることが分かった。温度上昇範囲が少し右方向にずれているのは、SiO2層の発熱エリアが右側10分の7の範囲である影響だと考えられる。現在、さらに解析の精度を上げ、現実により近いチップの発熱影響を調べるとともに、実装チップの改善を検討している。

#### 参考文献

[1] 丸山他、2013 年電子情報通信学会ソサイエティ大会予稿集、C-8-5 [2] 天谷他、2013 年電子情報通信学会ソサイエティ大会予稿集、C-8-3 [3] H. Yamamori, *et al.*, Supercond. Sci. Technol., vol. 21, p. 105007 (6), 2008.