## CeO<sub>2</sub>を用いた抵抗変化型メモリーにおける

## Ni Ge 下部電極に関する研究

Investigation of the NiGe bottom electrode in CeO<sub>2</sub> based ReRAM Devices 東工大フロンティア研<sup>1</sup>, 東工大総理工<sup>2</sup>, °金吉松<sup>1</sup>, 角嶋邦之<sup>2</sup>,

片岡好則<sup>2</sup>, 西山彰<sup>2</sup>, 杉井信之<sup>2</sup>, 若林整<sup>2</sup>, 筒井一生<sup>2</sup>, 名取研二<sup>1</sup>, 岩井洋<sup>1</sup> Tokyo Tech. FRC<sup>1</sup>, Tokyo Tech. IGSSE<sup>2</sup>, °J.Jin<sup>1</sup>,K. Kakushima<sup>2</sup>,

Y. Kataoka <sup>2</sup>, A. Nishiyama <sup>2</sup>, N. Sugii <sup>2</sup>, H. Wakabayashi <sup>2</sup>,

K. Tsutsui<sup>2</sup>, K. Natori<sup>1</sup>, H. Iwai<sup>1</sup>,

E-mail: jin.j.ac@m.titech.ac.jp

**Introduction** Resistive RAM (ReRAM), which is a strong candidate for the next generation of nonvolatile memory, still calls for new material technology because its problems in efficiency and reliability. Cerium oxide is promising for ReRAM application since it can be used as solid electrolyte having high dielectric constant and high ion conductivity [1]. In addition, cerium oxide is easy to react with NiGe, which modifies structure and concentration of vacancies in cerium oxide film. This work proposes a high On/Off ratio of CeO<sub>2</sub> based RRAM.

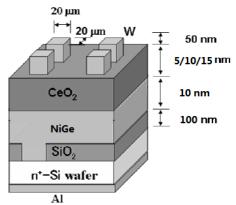

**[Experiment]** The structure of the devices is schematically shown in Fig.1. Fabrication started from growing a SiO2 layer on highly doped Si wafers by thermal oxidation, followed by formation of contact windows through SiO2 layer. After that, a NiGe bottom electrode layer, a CeO2 switching layer and a W bottom electrode layer were deposited in succession. Finally, Al was evaporated as a back contact followed by RTA in N<sub>2</sub> ambient for 30 s at 400 °C. Device with NiSi<sub>2</sub> as bottom electrode layer was also fabricated for comparison.

Fig.1. Schematic illustration of the RRAM device having W/CeO<sub>2</sub>/NiGe structure

--- Resistance 1E10 1E9 1E8 Resistance (ohms) 1E7 1000000 100000 10000 1000 100 10 40 60 80 Switching Cycle

Fig.2 the Switching process of W/CeO2 (5nm)/NiGe

**[Result]** The initial state of this device is low resistance satae and W/CeO<sub>2</sub> (5nm)/NiGe device shows the bipolar resistance switching behaviors. As shown in Fig.2, the ratio of high resistance state to low resistance state of this device takes an average value of about 10^5. On/Off ratio about 10^8 switching process was also observed.

[1] C. Lin, et al., Surface & Coating Technology 203, p.480-483, (2008)