# くし型電極を有するボトムコンタクト型 OFET のペンタセン膜厚依存性

Pentacene thickness dependence of OFET with interdigitated array electrodes 東工大総理工<sup>1</sup>, TMEC<sup>2</sup>, 分析工房<sup>3</sup>,

OFadliondi<sup>1</sup>,今井和雄<sup>2</sup>,籔本周邦<sup>3</sup>,佐藤芳之<sup>3</sup>,石原 宏<sup>1</sup>,大見俊一郎<sup>1</sup>

$To kyo\ Institute\ of\ Technology^1,\ TMEC\ (Thai\ Microelectronics\ Center)^2,\ Analysis\ Atelier\ Co.^3,$

°Fadliondi<sup>1</sup>, K. Imai<sup>2</sup>, N. Yabumoto<sup>3</sup>, Y. Sato<sup>3</sup>, H. Ishiwara<sup>1</sup>, S. Ohmi<sup>1</sup>

E-mail: fadli.o.aa@m.titech.ac.jp, ohmi@ep.titech.ac.jp

### 1. はじめに

単位面積当たりのゲート幅を大きくできるくし型電極を有するデバイスは、非破壊検査、通信、化学センシングなどの分野への応用が期待される周期的な電極構造である[1,2]。本研究では、くし型構造のソース/ドレイン電極を有するボトムコンタクト型 OFET に関してペンタセン膜厚依存性に関する検討を行ったので報告する。

### 2. 実験方法

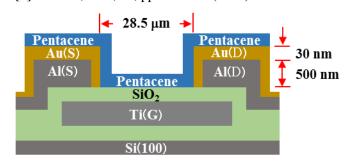

本研究で作製したボトムコンタクト型OFETの断面図を図1に示す。 $SiO_2/Si(100)$ 上に、Ti をゲート電極としてパターニングした。次にPECVD法により $SiO_2(600 \text{ nm})$ を形成した。次にAI電極(500 nm)を堆積後ゲート幅/ゲート長(W/L) $16000/28.5 \mu m$ のくし型構造をドライエッチングにより形成し、Au(30 nm)をめっき法で形成した。くし型構造は $355 \mu m \times 45$ 周期である。次に、蒸着法を用いてペンタセン膜厚を20 nm - 50 nmと変化させて室温で堆積した。堆積レートおよび堆積中の真空度はそれぞれ1.08 nm/minと $7.8 \times 10^{-6} \text{ Torr}$ とした。このように作製した試料に関して、電気特性を評価した。

# 3. 実験結果および考察

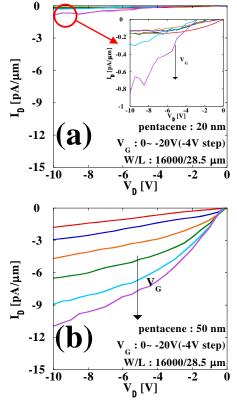

図 2(a)に、ペンタセン 20 nm を堆積した場合 の  $I_D$ - $V_D$  特性を示す。ドレイン電流が  $1 \text{ pA/\mu m}$  以下であることがわかった。

次に、ペンタセン 50 nm を堆積した場合の結果を図 2(b)に示す。ボトムコンタクト電極として用いた Au/Al 電極の垂直性により 50 nm に厚くした場合に良好な  $I_D$ - $V_D$  特性が得られることが分かった。

#### 謝辞

本研究にご協力いただいた日立中央研究所の藤崎芳久氏に感謝致します。

## 参考文献

[1]Mamishev et al., IEEE, **92**, pp. 808-845 (2004). [2]Jae et al., ECS, **12**, pp. 285-287 (2009).

図1 くし型電極ボトムコンタクト型 OFET の デバイス構造

図 2  $I_D$ - $V_D$ 特性のペンタセン膜厚依存性。 (a) 20 nm、(b) 50 nm。