# Effects of Annealing Ambient on the Electrical Properties of HfN Gate Insulator

## Formed by ECR Plasma Sputtering

Tokyo Institute of Technology, "Nithi Atthi, Dae-Hee Han, and Shun-ichiro Ohmi

E-mail: atthi.n.aa@m.titech.ac.jp, ohmi@ep.titech.ac.jp

### 1. Introduction

Scaling down an equivalent oxide thickness (EOT) of high- $\kappa$  gate insulator beyond 0.5 nm is a great challenge for next generation CMOS technology because of the formation of an interfacial layer (IL) between high- $\kappa$ /Si interface. The IL with low dielectric constant increases the EOT [1]. We have reported that the 0.5 nm EOTs were obtained by using hafnium nitride (HfN) gate insulator formed by electron-cyclotron-resonance (ECR) plasma sputtering on both Si(100) and Si(110) substrates [2].

In this paper, the effect of annealing ambient dependence on the electrical characteristics of HfN gate insulator was studied. The effects of surface orientation including p-Si(100) and p-Si(110) were investigated for three-dimensional MOSFET device.

#### 2. Experimental Procedure

First, p-Si(100) and p-Si(110) substrates were cleaned by SPM and DHF. Then HfN film (4 nm) was deposited by ECR plasma sputtering with the gas pressure of 0.20 Pa (Ar/N<sub>2</sub>: 20/8 sccm) [3,4]. The deposited HfN films were annealed in the Ar/4.9%H<sub>2</sub> and N<sub>2</sub>/4.9%H<sub>2</sub> forming gas (FG) ambient with the flow rate of 1 SLM at 500-600°C for 10-20 min. Finally, Al electrode ( $\phi$ = 94 µm) was deposited by evaporation through a shadow mask. The C-V and J-V characteristics of Al/HfN/p-Si MIS diodes were measured. The density of interface states (D<sub>it</sub>) was evaluated by Terman method.

#### 3. Results and Discussion

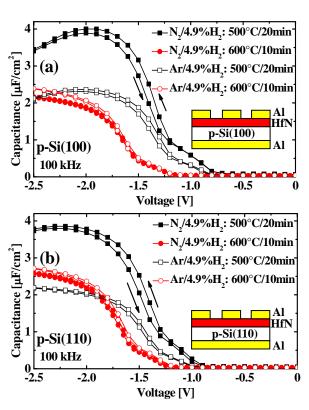

Figures 1(a) and 1(b) show the C-V characteristics (100 kHz) of Al/HfN/p-Si(100) and Al/HfN/p-Si(110) MIS-diode, respectively. The N<sub>2</sub>/4.9%H<sub>2</sub> FG annealing has better capability for hydrogen passivation at the HfN/Si interface and/or in the HfN film on both Si(100) and Si(110) surface compared to Ar/4.9%H<sub>2</sub> FG annealing. By using N<sub>2</sub>/4.9%H<sub>2</sub> FG annealing at 500°C/20 min, similar C-V characteristics with an EOTs of 0.47 and 0.51 nm with leakage current density,  $J_{\rm g},\,(@V_{FB}\,\mbox{--}1\,\,V)$  of 1.1 and 1.4 A/cm<sup>2</sup> were obtained on Si(100) and Si(110) substrates, respectively. By annealing the samples in Ar/4.9%H<sub>2</sub> FG ambient at 600°C/10 min, EOTs of 1.0 and 0.82 nm with low  $J_g(@V_{FB}-1 V)$  of  $3.9 \times 10^{-5}$  and  $6.4 \times 10^{-5}$  A/cm<sup>2</sup> were obtained on Si(100) and Si(110) substrates, respectively. The  $D_{it}$ with the order of  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> was obtained on both substrates after annealed in both FG ambients.

Fig. 1. C-V characteristics of Al/HfN/p-Si (100 kHz) annealed in Ar/4.9%H<sub>2</sub> and N<sub>2</sub>/4.9%H<sub>2</sub> FG ambient at 500°C/20 min and 600°C/10 min. (a) Si(100) and (b) Si(110).

#### 4. Conclusions

We investigated an effect of annealing ambient dependence on the diode characteristic of HfN gate insulator formed by ECR plasma sputtering. The EOTs below 0.5 nm were obtained on both Si(100) and Si(110) substrates by  $N_2/4.9\%H_2$  FG annealing at 500°C/20 min.

#### Acknowledgements

The authors would like to thank Prof. Emeritus H. Ishiwara of Tokyo Institute of Technology, Prof. Emeritus T. Ohmi and Dr. T. Suwa of Tohoku university, and Dr. M. Shimada and Mr. I. Tamai of MES-AFTY for their support.

#### References

- [1] Y. Morita, et. al., Appl. Phys. Lett., 2 (2009) 011201-1.

- [2] N. Atthi, et. al., The 74<sup>th</sup> JSAP autumn meeting (2013) 17p-B5-9.

- [3] H.-S. Han and S. Ohmi, IEICE Electron. Express, 9 (2012) 1329.

- [4] N. Atthi, et. al., JSAP-MRS joint symposia, (2013) 18p-PM1-32.