18p-D8-14

## 低界面準位と sub-nm CET を有する La<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As ゲートスタックの実現 Low D<sub>it</sub> La<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As Gate Stack scaled to sub-nm CET

東エ大フロンティア研<sup>1</sup>,東工大総理工<sup>2</sup> <sup>0</sup>ハサンザデ ダリューシュ<sup>1</sup>,大嶺洋<sup>1</sup>,角嶋邦之<sup>2</sup>, 片岡好則<sup>2</sup>,西山彰<sup>2</sup>,杉井信之<sup>2</sup>,若林整<sup>2</sup>,筒井一生<sup>2</sup>,名取研二<sup>1</sup>,岩井洋<sup>1</sup>

Tokyo Tech. FRC<sup>1</sup>, Tokyo Tech. IGSSE<sup>2</sup> °D. Hassan Zadeh<sup>1</sup>, H. Oomine<sup>1</sup>, K. Kakushima<sup>2</sup>, Y.

Kataoka<sup>2</sup>, A. Nishiyama<sup>2</sup>, N. Sugii<sup>2</sup>, H. Wakabayashi<sup>2</sup>, K. Tsutsui<sup>2</sup>, K. Natori<sup>1</sup>, , H. Iwai<sup>1</sup>

## E-mail: zade.d.aa@m.titech.ac.jp

[Introduction] Integration of high-mobility channels such as InGaAs is envisaged for beyond 10-nm node devices [1]. However, fabrication of high quality high-k/III-V interface with low interface trap density remains a key issue. Overwhelming majority of InGaAs device demonstrations use Al<sub>2</sub>O<sub>3</sub> as gate dielectric, which benefits from good interface properties. Consequently scaling of InGaAs-based gate stacks has been limited due to low k-value (~9) of Al<sub>2</sub>O<sub>3</sub>. However, high Cox values in quasi-ballistic regime of 10-nm node and beyond is required to minimize the effect of high semiconductor capacitance and improve gate controllability [2]. In this study, we have demonstrated a scalable La<sub>2</sub>O<sub>3</sub>/InGaAs gate stack with La<sub>2</sub>O<sub>3</sub> deposited either by EB or ALD methods with equal interface quality, thanks to the formation of an amorphous interfacial layer at the La<sub>2</sub>O<sub>3</sub>/InGaAs interface.

[Experiments] La<sub>2</sub>O<sub>3</sub>-gated devices were fabricated on *n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As substrates (dopant:  $1.0 \times 10^{16}$  cm<sup>-3</sup>). Substrates were first, treated by HF and (NH<sub>4</sub>)<sub>2</sub>S (6%) solution prior to La<sub>2</sub>O<sub>3</sub> deposition. ALD-La<sub>2</sub>O<sub>3</sub> films were grown from precursors lanthanum tris(isopropylcyclopentadienyl) and H<sub>2</sub>O at various deposition temperatures. Bi-layer TiN/W metal gates were in-situ deposited by RF sputtering. A gate last scheme was used to fabricate InGaAs MOSFETs on *p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As (dopant:  $1.8 \times 10^{17}$  cm<sup>-3</sup>) with a similar gate stack process flow to capacitors.

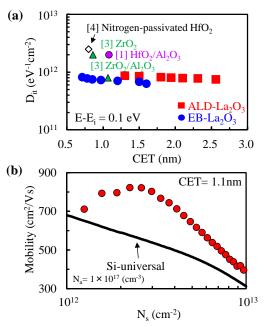

[Results] Conductance measurements were carried out to evaluate the interface trap density ( $D_{it}$ ) at La<sub>2</sub>O<sub>3</sub>/InGaAs interface. The results compared to other recently reported high-k materials is shown in Fig. 1 (a). Small  $D_{it}$  on the order of  $10^{11}$  (cm<sup>-2</sup> eV<sup>-1</sup>) is achieved for La<sub>2</sub>O<sub>3</sub>/InGaAs capacitors even at sub-nm CET values. The similarity of results between deposition methods can be attributed to the presence of interfacial layer in the form of LaInGaO<sub>x</sub> which is formed reactively at InGaAs interface. InGaAs MOSFET operation with ALD-La<sub>2</sub>O<sub>3</sub> as gate dielectric and Ni as metal S/D is demonstrated in Fig. 1(b). Mobility exceeding that of Si-universal is achieved for a gate stack with CET= 1.1 nm.

Fig.1 (a)  $D_{it}$  dependence on CET for La<sub>2</sub>O<sub>3</sub>/InGaAs and (b) effective electron mobility of nMOSFETs measured by split C-V.

## [References]

S. Takagi et al., IEDM 505(2012). [2] M. Fischetti et al., IEEE Trans. Electron. Devices, 54, 2116(2007).

V. Chobpattana et al., Appl. Phys. Lett. 102, 022907(2013). [4] J. Huang et al., IEDM 335(2009).

[Acknowledgement] This work was granted by JSPS through FIRST program initiated by the CSTP.