## High-k ゲートスタック開発を振り返って

## What were the key points in the development of high-k gate stacks ○白石 賢二(名大院工)

°Kenji Shiraishi (Nagoya University)

E-mail: shiraishi@cse.nagoya-u.ac.jp

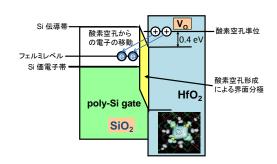

**はじめに:** ハフニア系絶縁膜において、2003 年当時最も深刻な問題として知られていたのは、p+poly Si ゲートを用いた MISFET の Vth シフトが異常に大きくなり (Fermi Level Pinning)、CMOS を設計する上で大きな問題が生じていたことである[1]。これは、high-k ゲートスタック開発にとって、乗り越えなければならない問題であった。この大きな Vth シフトを説明する説として、当時界面 Hf-Si ボンド形成説[1]等が提案されていたが、統一的な理解は至らなかった。我々は  $HfO_2$  がイオン結晶であるという最も基本的な事実に注目し、p+poly Si ゲートで観測される大きな Vth シフトの起源は  $Si/HfO_2$  界面の酸素空孔を生成する界面反応の熱力学によって Vth シフトが決定されるという「酸素空孔モデル」を 2004 年に提案し(図1)、その後の high-k ゲートスタック開発を先導する知見を得た[2]。

**High-k ゲートスタック開発のその後:**その後、high-k ポリシリコンゲート技術から一気に high-k 金属ゲート技術に舵を切った high-k ゲートスタック技術においても、「酸素空孔モデル」は 大きな指針となっていった。実際赤坂らによって、界面 SiO₂層が薄いときには金属ゲートで も生じる Fermi Level Pinning も「酸素空孔モデル」によって基本的に説明されることが指摘された[3]。一方、岩本ら鳥海教授のグループは  $HfO_2$  と他の絶縁体  $(Al_2O_3, SiO_2$  等) が接触することで絶縁体同志の界面に界面ダイポールが生じることを発見し、閾値制御に筋道をつけた[4]。その後、当時パナソニックの丹羽らは閾値にゲート幅依存性があることを見出した。このゲート幅依存性を用いて丹羽らは汎用の high-k 金属ゲートの LSI の量産化を実現することになる。ゲート幅を大きくして high-k ゲートスタックまでの距離を長くすると外部からの酸素が界面まで到達しないため、Fermi Level Pinning が起こったままになってしまって pMOSFET 的な振る舞いをする。これに対してゲート幅を小さくして high-k ゲートスタックまでの距離を短くすると外部からの酸素が界面まで到達するため、Fermi Level Pinning が解消されて nMOSFET 的な振る舞いになる。このようにゲート幅の異なる MOSFET を作りこむことで、pMOSFET と nMOSFET を作り分けることができるようになった。この技術を用いてパナソ

ニックが汎用 high-k 金属ゲート LSI 量産化の世界第一号となった[5]。

講演ではさらに、high-k ゲートスタック開発において物理学、さらには計算科学が果たした役割についても議論する予定である。

[1] C. Hobbs *et al.*, VLSI 2003. [2] K. Shiraishi *et al*, VLSI 2004., K. Shiraishi *et al.*, Jpn. J. Appl. Phys. 2004. [3] Y. Akasaka *et al.*, Jpn. J. Appl. Phys. 2006. [4] K. Iwamoto *et al.*, Appl. Phys. Lett. 2008. [5] M. Niwa, "High Permittivity Gate Dielectric Materials", Springer 2013.

図 1: Si と  $HfO_2$  が接触すると Si が  $HfO_2$  を還元し、 $HfO_2$  中に酸素空孔が形成される。この酸素空孔から Si 側に電子が移動し、フェルミレベルは Si と  $HfO_2$  の界面反応で決まる固有の位置にピニングされる。