# Effective reduction of parasitic resistance in Ge p-MOSFETs by ion implantation after

## germanidation technique

# <sup>0</sup>張文馨,太田裕之,前田辰郎(産総研)

## <sup>°</sup>Wen Hsin Chang, Hiroyuki Ota, Tatsuro Maeda (AIST)

#### E-mail address: wh-chang@aist.go.jp

Ge has been considered as a very promising channel material for replacing Si due to its higher carrier mobility than that of Si. Much improvement has been reported for Ge-based MOS devices over the past decade. However, it is still very challenging to achieve ultra-shallow junction as well as ultra-low parasitic resistance on Ge MOS devices. With an appropriate drive-in annealing, ion implantation after germanidation (IAG) technique has been considered an effective way to form ultra-shallow junction without Fermi level pinning (FLP) at metal/Ge interface.<sup>1,2</sup> To investigate the impact on device performances by IAG technique, in this work, Ge *p*-MOSFETs with self-aligned metallic NiGe S/D formed by IAG technique were fabricated. With increasing drive-in annealing temperature, effective reduction in parasitic resistance ( $R_{para}$ ) of Ge *p*-MOSFET was demonstrated.<sup>3</sup>

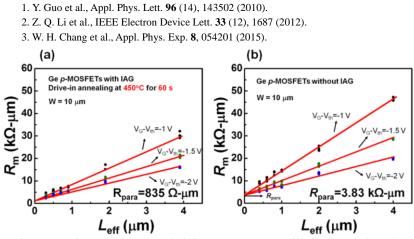

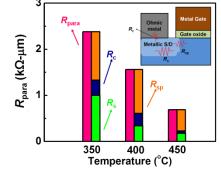

The relationship between measured resistivity ( $R_m$ ) and effective gate length ( $L_{eff}$ ) for varying gate overdrive values of Ge *p*-MOSFETs fabricated with and without IAG technique is shown in Fig. 1 (a) and (b).  $R_{para}$  reduced about five times for the devices fabricated with IAG technique and low  $R_{para}$  of 835  $\Omega$ -µm was achieved on Ge *p*-MOSFETs after 450 °C drive-in annealing. The components in  $R_{para}$  for the Ge *p*-MOSFETs have been analyzed and summarized in Fig. 2. The reduction of  $R_{para}$  is actually by means of the decrease for both sheet resistance ( $R_s$ ) and spreading resistance ( $R_{sp}$ ). It is noted that high temperature annealing has benefits in IAG technique, which helps to decrease the  $R_{para}$  in Ge *p*-MOSFETs while the thermal stability of the whole gate stack has to be considered for achieving high mobility channel as well as low  $R_{para}$ .

In conclusion, we demonstrate the effect of IAG technique in the device performance of Ge *p*-MOSFETs with the low  $R_{para}$  of 835  $\Omega$ -µm. The results can be readily applied to future Ge *p*-MOSFETs for achieving shallow junction and low parasitic resistance.

The authors would like to thank the support from N. Hata, M. Yamazaki, and K. Masuda in Nano-Processing Facility, AIST-NPF. W. H. Chang would like to thank the Ministry of Science and Technology in Taiwan for its financial support under Grant No. 104-2917-I-564-042 **References**

Fig. 1 Device measured resistivity  $(R_m)$  versus effective gate length  $(L_{\text{eff}})$  at varying gate overdrives for Ge *p*-MOSFETs fabricated (a) with and (b) without IAG technique. The line intersects at one point gives the value to parasitic resistance  $(R_{\text{para}})$ .

Fig. 2 Summary of  $R_{\text{para}}$ ,  $R_{\text{s}}$ , contact resistance  $(R_{\rm c})$ and  $R_{\rm sp}$ for Ge p-MOSFETs fabricated by IAG technique with different drive-in annealing temperatures. The inset shows the simple schematic diagram for a self-aligned metallic S/D MOSFET, with  $R_{\rm c}$ ,  $R_{\rm s}$  and  $R_{\rm sp}$  indicated.