## 自立 GaN 基板上 p-n 接合ダイオードの初期耐圧不良解析(2)

An initial failure analysis of the low breakdown voltage of GaN p-n diodes fabricated on free-standing GaN substrates (2)

○成田 好伸 ¹、堀切 文正 ¹、吉田 丈洋 ¹、太田 博 ²、三島 友義 ²、中村 徹 ²

(1. サイオクス、2. 法政大)

°Y. Narita<sup>1</sup>, F. Horikiri<sup>1</sup>, T. Yoshida<sup>1</sup>, H. Ohta<sup>2</sup>, T. Mishima<sup>2</sup>, T. Nakamura<sup>2</sup> (1.Sciocs Co. Ltd., 2.Hosei Univ.)

E-mail: yoshinobu-narita@ya.sumitomo-chem.co.jp

## <u>1. はじめに</u>

GaN 自立基板上に縦型 p-n 接合ダイオードの試作を行い、初期耐圧不良の原因調査を行った結果、素子内に表面ピットが存在している場合、逆方向耐圧特性が著しく低下することを確認した [1]。そこで本研究では、その表面ピットの発生源について調査を行った。

## 2. 実験及び結果

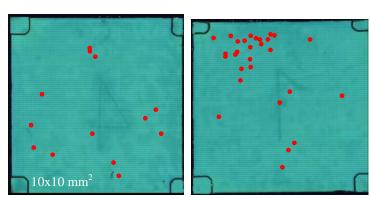

10mm 角の GaN 自立基板を 2 枚用意し、MOVPE 法により p-n 接合構造の成長を同一条件で 2 回行った。 1 回目の成長では新品の基板ホルダーを使用し、 2 回目の成長ではデポ物をクリーニングした後のホルダーを使用して成長を行った。その結果、 1 回目の成長では面内に 13 個のピットが発生し、 2 回目の成長ではその倍の 29 個のピットが発生した。なお、使用した基板にはあらかじめピットの発生源になりえるインバージョンドメインがないことを確認している。

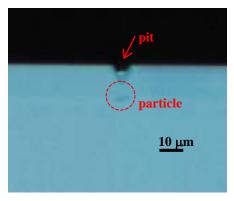

図1に、ピットの発生位置にマーキングを施したエピの外観写真を示す。同一条件で成長したにもかかわらずピットの発生数に差が生じたのは、ホルダーの清浄度の違いによるものではないかと考え、ピットの発生源を確認するため、エピを割ってピットの断面を光学顕微鏡にて観察した。その結果、図2に示す通り、ピット下部に異物が存在していることが分かった。異物の位置は概ねエピの総膜厚の約15.5μmと同程度であるため、異物は基板表面に付着したものと推察され、ピットは付着した異物を避けるように結晶成長が行われた結果、発生したものと考えられる。

これらの結果から、異物の付着を防ぐような基板及び炉内清浄度の管理を行うことでピットの発生が抑制され、p-n 接合ダイオードの初期耐圧不良を改善することが可能と思われる。

本研究は環境省「未来のあるべき社会・ライフスタイルを創造する技術イノベーション事業」 の委託を受けてなされた。

Fig.1. Surface images of the GaN p-n junction epitaxial wafers. Pits are marked by red circles. (left: the 1st growth, right: the 2nd growth)

Fig.2. Cross-sectional microscopic image of the pit.

[1] 堀切ら、第76回応用物理学会秋季学術講演会(本報告の1件前を予定)