## 最先端 CMOS 加工におけるダメージの予測・制御技術

## Prediction and Control Technology for Etching Damage on Advanced CMOS

ソニー(株) 〇久保井 信行, 深沢 正永, 辰巳 哲也

Semiconductor Device Development Division, DMRG, RDS Platform, Sony Corporation

°Nobuyuki Kuboi, Masanaga Fukasawa, Tetsuya Tatsumi

E-mail: Nobuyuki.Kuboi@jp.sony.com

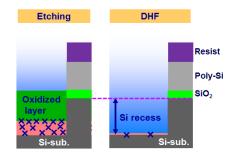

プラズマエッチングによるトランジスタのゲートやサイドウォールの加工においては、プロセ ス中の入射水素イオンに起因する Si 結晶欠陥層(ダメージ層)が生成する。このダメージ層は後 工程のウェット(DHF)処理で酸化除去されるが、この際、いわゆるSi リセスが発生することが 報告されている[1]。これまでのイオンビーム実験[2]や分子動力学計算[3]等の研究によって、下地 ゲート酸化膜に対する高選択比での加工にも関わらず、下地ゲート酸化膜を貫通し、Si 基板内の 数 10nm もの深い領域に水素イオンが侵入し、ダメージを生成することがわかってきた。しかも、 このダメージは、従来のアニール処理でも十分に回復しない場合がある[4]。さらに、ウェット処 理によって表層数 nm のダメージ層は酸化除去されるが、この除去による Si リセス深さおよびさ らに深い残留ダメージ(図1)は、 $V_{th}$ や  $I_{off}$ 等のデバイス特性、特に、FinFET に代表される最先 端CMOSデバイス特性により深刻な影響を与えうることがデバイスシミュレーションで示されて いる[5]。そのため、元となるエッチングダメージの予測・制御は非常に重要である。

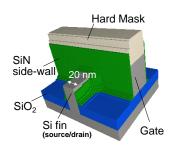

これまでは、Planer 型 MOS を模擬して実験等が進められてきたが、最先端 CMOS 特有の複雑 な3次元構造やパターン側面のダメージの解析には3次元シミュレーションが必須となる。また、 FinFET 加工を考えた場合、ソース/ドレイン領域である Si fin 上に積まれたサイドウォールとなる SiN 膜加工がキープロセスとなるが、シミュレーションに必要となる SiN 表面反応モデル構築は 未達成であった。そこで、我々は、SiN 膜加工の表面反応を新規モデル化し、そのモデルを実装 した独自の3次元形状・ダメージシミュレーションの開発を行った[6]。本講演では、エッチング ダメージ生成の機構、SiN 表面反応のモデル化、FinFET を想定したエッチングシミュレーション 結果(図2)について議論したい。

## [参考文献]

- [1] Ohchi et al., JJAP 47 (2008) 5324

- [3] Miyake et al., JJAP 53 (2014) 03DD02 [4] Fukasawa et al., DPS 2014

- [5] Eriguchi et al., DPS 2013

- [2] Ito et al., JVST A29 (2011) 050601

- [6] Kuboi et al., DPS 2014

図 1: DHF 前後のダメージ分布

図2: FinFET 加工を想定したシミュレーション結果