## 裏面コンタクト型ヘテロ接合 Si 結晶セルにおける裏面構造の 幾何寸法設計指針の検討

Guideline for Back-Contact Design of Interdigitated Back-Contact Si Heterojunction Solar Cells

O<sup>(PC)</sup>神岡 武文 <sup>1</sup>、林 豊 <sup>1</sup>、中村 京太郎 <sup>2</sup> 、大下 祥雄 <sup>2</sup> (1. 豊田工大、2. 明治大)

<sup>(PC)</sup>Takefumi Kamioka <sup>1</sup>, Yutaka Hayashi <sup>2</sup>, Kyotaro Nakamura <sup>2</sup>, Yoshio Ohshita <sup>2</sup>

(1.Toyota Technol. Inst., 2.Meiji Univ.)

E-mail: t-kamioka@toyota-ti.ac.jp

[はじめに] 裏面コンタクト型へテロ接合 Si 結晶セル(interdigitated back-contact Si heterojunction; IBC-SHJ cell)は、25%超の変換効率が達成されたこともあり[1,2]、高効率セルとして注目を集めている。しかし、量産への移行には課題が残る。その1つに、緩和されたデザインルール下での最適設計指針の獲得がある。裏面コンタクト型ではエミッタとコレクタが効率に寄与しないギャップを介して配置されるため、ギャップの幅やパッシベーション品質などの影響を考慮した議論が必要となる。今回は、前回の報告を踏まえ[3]、ギャップ領域のパッシベーション品質の重要性をデバイスシミュレーションにより調査した結果を報告する。

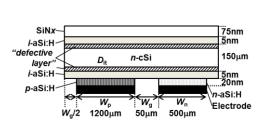

**[シミュレーション方法]** 図 1 に、今回シミュレーションした n 型基板の IBC-SHJ セルのデバイスモデルを示す。物理モデルや各材料の物性値は先行研究[3-5]に従った。結晶/アモルファス(c/a)Si 界面の欠陥が多く存在する領域を再現するため、界面の cSi 側に 1 nm 厚の"defective layer"を仮定し、この領域の界面準位密度( $D_{it}$ )をモデリングしている。2 次元デバイスシミュレータ("Atlas"、Silvaco 社製)を用い、 $D_{it}$ や電極間ギャップ幅がセル性能に与える影響を解析した。

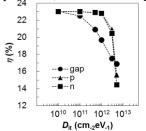

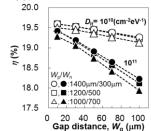

**[結果および考察]** 図 2 は、裏面側 c/a 界面の各領域(ギャップ、i/p 積層構造直下、i/n 積層構造直下)における  $D_{it}$  の影響を示したものである。どの領域でも  $D_{it}$  増加にともない変換効率は低下するが、比較的小さい  $D_{it}$  で影響が顕在化するという点で、ギャップ領域の影響がもっとも大きい。ギャップ領域のパッシベーション品質を高めることが最重要であることを示している。図 3 は、 $D_{it}$  やエミッタ被覆率をパラメタとして得られた、変換効率のギャップ幅依存性を示したものである。エミッタ被覆率よりも、ギャップ幅やパッシベーション品質の影響が極めて大きいことがわかる。量産プロセスのようにギャップ幅を狭くできない場合、i-aSi:H 層によるパッシベーション品質をできるだけ高めることが優先される。

[謝辞] 本研究の一部は NEDO の支援を受けて実施された。

[参考文献] [1] K. Masuko *et al.*, Tech. Dig. PVSC (2014). [2] J. Nakamura *et al.*, Tech. Dig. PVSC (2014). [3] 神岡他, 2014 年第 75 回秋季応物, 17pA25-12. [4] Y. Hayashi *et al.*, IEEE J. Photovoltaics **3** (2013) 1149. [5] Z. Shu *et al.*, Prog. Photovolt. Res. Appl. (2013), DOI:10.1002/pip.2400.

図 1. IBC-SHJ セルのデバイスモデル.

図 2. 変換効率( $\eta$ )の界面 準位密度( $D_{ij}$ )依存性.

図 3. 変換効率(η)のギャップ 幅(W<sub>o</sub>)依存性.