## In-Plane Gate デバイスの電流 - 電圧特性

<sup>°</sup>Sho Sakamoto<sup>1</sup>, Kouzi Onomitu<sup>2</sup>, Hideki Yamamoto<sup>2</sup>, Yosiji Horikosi<sup>1</sup>, Tosiki Makimoto<sup>1</sup>

(1.Waseda Univ., 2.NTT BRL)

## E-mail: justdoit@ruri.waseda.jp

<u>はじめに</u>: 我々は、二次元電子構造を加工して製作する in-plane-gate (IPG) デバイスの研究を行っている[1]。このデバイスは半導体ウエハにトレンチを形成しただけで製作が可能であり、その構造とプロセスの簡潔さから、IPG デバイスの高集積化が期待できる。動作原理は、ゲート電圧を印加し、トレンチを介した静電効果によりチャネル部の空乏層を制御することでチャネルの開閉を行うというものである。これまで我々は、IPG デバイスにおいて負性微分抵抗が発現し、その特性がチャネルの長さと幅によって変化することを確認してきた[2]。これらの過程で、チャネルの形状によって電気特性が変化することを確認できたため、チャネルの形状がデバイス応用上重要であると考えた。そこで今回、チャネル形状の異なる IPG デバイスを製作し、トランスコンダクタンスの変化を調べた。

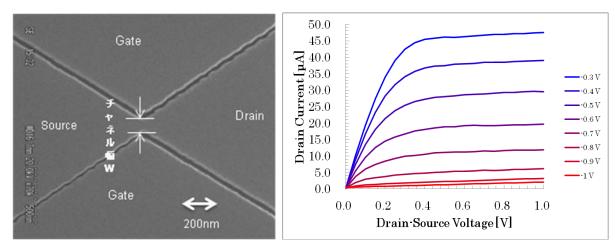

実験結果と考察: Ino.53Gao.47As / Ino.52Alo.48As 二次元電子構造ウエハ上に電子線描画でマスクパターンを形成し、RIEエッチングを行い、IPGデバイスを製作した。製作した構造の一例に対するSEM 像をFig. 1 に示す。また、室温におけるI-V特性をFig. 2 に示す。Fig. 2 に示したように、ノーマリーオン型のトランジスタ特性が得られた。そして、Fig. 2 よりトランスコンダクタンスを求めたところ、チャネル幅80nmのIPGデバイスにおけるトランスコンダクタンスの最大値は30  $\mu$  Sであった。

Fig. 1. SEM image of the IPG device Fig. 2. The I-V characteristics of the IPG devices (RT)

- [1]Y. Komatsuzaki, T. Kyougoku, K. Saba, K. Onomitsu, H. Yamaguchi, and Y. Horikoshi, Phys.Status Solidi C 9, 385-388, 2012.

- [2] Y. Komatsuzaki, K. Higashi, T. Kyougoku, K. Onomitsu, and Y. Horikoshi, Phys. Status Solidi C 8, 408-410, 2011.