# 超格子 FET に向けたダブルバリア p-i-n 接合ダイオード

Double barrier p-i-n junction diode for Superlattice FET

<sup>○</sup>行待 篤志¹、柏野 壮志¹、宮本 恭幸¹ (1. 東工大院理工)

°Atsushi Yukimachi<sup>1</sup>, Masashi Kashiwano<sup>1</sup>, Yasuyuki Miyamoto<sup>1</sup> (1.Tokyo Tech)

E-mail: yukimachi.a.aa@m.titech.ac.jp

#### 研究背景

従来の MOSFET ではその構造上、室温においてサブスレッショルド領域における電流変化(SS)が 60mV/dec に制限されてしまうため、それによって高速省電力化が妨げられている。そこで、60mV/dec よりさらに急峻な SS が得られる FET として、ソースに超格子構造を取り入れた FETが提案されている[III2]。しかし、この FET に関する報告は数値計算にとどまっており、実験的に関室報告させたという報告は無い。そこで、その超格子 FET の室温動作のための第一歩として、カソードにダブルバリアを取り入れて電子をエネルギーでフィルタリングできることを確認し、60mV/dec を下回る急峻な I-V 特性を観測することを目標に実験を行った。

### 素子構造決定と素子作製

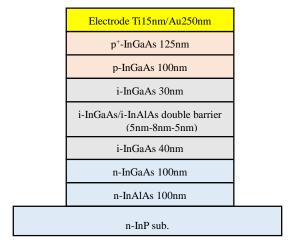

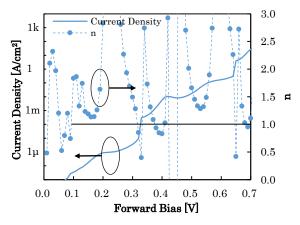

簡単のため p 領域と n 領域の間の伝導帯を直線的に結んだモデルで伝搬行列法によって透過率を計算し、I-V 特性を見積もって決定した。その素子構造が Fig. 1 である。井戸幅は 8nm、障壁幅は 5nm のダブルバリア構造で、数値計算では Fig. 2 の通り n 値が 1 を下回った。

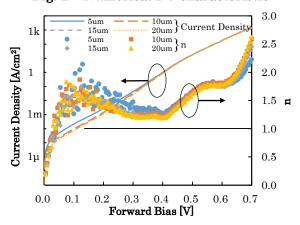

そして実際に MOVPE 装置を用いてこの層構造を基板に成長し、5,10,15,20μm 角の 4 種類のサイズの正方形の断面の素子を作って測定を行った。

# 測定結果

Fig. 3 より n 値が 1 を下回るような素子はなかった。しかし、0.31V 付近と 0.40V 付近に n 値が小さくなるくびれのような特性が得られ、その位置は Fig. 2 の数値計算の結果の位置に概ね一致する。そのことからその n 値のくびれはこのダブルバリアによる量子効果であると考えられる。

また、小さな素子のほうが電圧 0.1-0.4V 付近で n 値が大きくなってしまっていることがわかる。これは、小さな素子のほうが素子面積に対して周辺長が長くなるので、表面再結合による電流の割合が増えたためだと考えられる。よって、表面状態を改善することで全体的に n 値をさらに下げられると言える。

#### 謝辞

本研究は日本学術振興会科学研究費補助金の補助を受けて行われた

# 参考文献

- [1] E. Gnani, P. Maiorano, S. Reggiani, A. Gnudi and G. Baccarani: IEDM (2011) 5.1.1.

- [2] M. Kashiwano, A. Yukimachi and Y. Miyamoto: SSDM (2013), D-7-3

Fig. 1 Fabricated double barrier PIN diode

Fig. 2 Numerical I-V characteristic

Fig. 3 Experimental I-V characteristic