## 引っ張り歪み GOI の CMP 薄膜化による発光強度増大

Light Emission Enhancement from Tensile-Strained Ge-on-Insulator (GOI) by CMP Thinning

○橋本秀明、徐学俊、澤野憲太郎、丸泉琢也(都市大総研)

<sup>O</sup>Hideaki Hashimoto,Xuejun Xu,Kentarou Sawano, Takuya Maruizumi (1.Tokyo City Univ.)

E-mail: g1115075@tcu.ac.jp

## 1. はじめに

チップ内光集積回路(OEIC)の実現に向け Ge が注目されており、特に Si 基板上に Ge をエピ成長させることで、Ge に引っ張り歪みが導入され、直接遷移化による発光効率増大につながる。Ge/Si 界面近傍では、歪み緩和に伴う転位などの欠陥が多く存在するが、貼り合わせ法による Ge-on-Insulator (GOI) 構造を形成することで、欠陥領域を除去することができる。本研究では、CMP により歪み GOI の Ge 層の膜厚を変化させ、室温下での発光特性評価を行った。

## 2. 実験方法

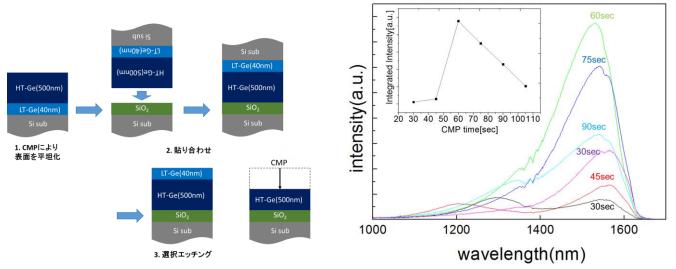

試料構造を図.1 に示す。固体ソース MBE を用いて、Si(100)基板上に成長温度( $T_g$ ) 350 $^{\circ}$ Cにて 40 nm の LT-Ge 層を成長し、その後  $T_g = 600^{\circ}$ Cにて 500 nm の HT-Ge 層の成長を行った。成長した Ge 層を SiO<sub>2</sub>/Si 支持基板 に貼り合わせ、700 $^{\circ}$ C、1 時間のアニール処理、Si 層の研磨と選択エッチングによる除去により、GOI 構造とした。その後、CMP により Ge 層の膜厚を徐々に研磨しながら、その都度室温 PL 評価を行った。

## 2. 結果及び考察

各 CMP 研磨時間における PL スペクトルを図.2 に示す。1400~1600 nm の範囲で強い発光が確認でき、歪 みの効果によって直接遷移の寄与が増大していることを示している。PL 強度の CMP 時間変化を比較すると、いったん強度が増加し、その後減少していることが分かる。これは、初めに欠陥を多く含む Ge 層が完全に除去され、非発光再結合が効果的に抑制でき、その後は Ge 層の体積減少により発光強度が減少したものと考えられる。つまり、GOI 化による欠陥層除去と、Ge 層膜厚の最適化によって高い発光強度を持つ GOI を得ることができることが示された。

本研究より、欠陥を含む Ge 層は GOI の発光を妨げるものであり、Ge を発光素子として用いる場合除去することが望ましいと考える。

本研究の一部は、文部科学省私立大学戦略的研究基盤形成支援事業、科学研究費補助金、総務省 SCOPE プロジェクトの支援を受けて行われた。

図1 試料構造

図2 各 CMP 時間における室温 PL スペクトルと積分強度