## SiO<sub>2</sub>注入マスクを用いた6インチ基板上の高エネルギーイオン注入技術開発

High energy ion implantation process on 6 inch 4H-SiC substrates using SiO<sub>2</sub> mask 住友電気工業(株)

O堀井 拓、久保田 良輔、和田 圭司、田中 聡、関口 剛、御神村 泰樹

Sumitomo Electric Industries, Ltd.

°T. Horii, R. Kubota, K. Wada, S. Tanaka, T. Sekiguchi, and Y. Mikamura E-mail: horii-taku@sei.co.jp

【緒言】SiC デバイスの作製ではイオン注入、活性化アニールや電極形成用合金化が必要となるなど、Si とは異なり高温の熱処理を伴う。特に、高ドーズのイオン注入では基板を加熱する高温イオン注入が行われるため、注入マスクとしては  $200\sim600$   $^{\circ}$   $^{\circ}$  Cに耐え得る材質が求められる。近年 SiC 超接合デバイスの研究も行われており、注入阻止能の高い注入マスクの安定形成が望まれている  $^{(1)}$  。本報告では、量産性に優れる TEOS(Tetra-Ethyl-Ortho-Silicate)原料の  $SiO_2$  膜を注入マスクとして用い、高エネルギー注入を可能にする注入阻止能、及び 6 インチ基板上で面内均一性を検証した結果について報告する。

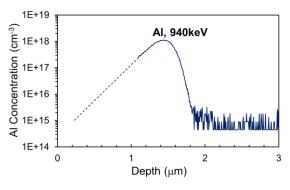

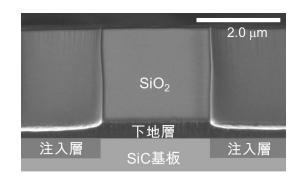

【実験】LP-CVD 法により TEOS 原料を用いて  $SiO_2$  膜を 6 インチ SiC 基板上に堆積した後、基板温度を  $500^\circ$ Cに加熱し、注入エネルギー940 keV の Al イオン注入を行った。 $SiO_2$  膜の注入阻止能を検証するために、SIMS 分析により  $SiO_2$  中の Al 濃度の深さ分布を測定した。また、 $SiO_2$  膜を RIE により加工し、注入 マスクとして用いて、6 インチ n 型  $4^\circ$  オフ 4H-SiC(0001) 基板上に DMOSFET を作製し、評価を行った。 【結果】図 1 は 940 keV の Al イオン注入を行って  $SiO_2$  膜中の Al 濃度深さ分布を検証したものであり、約  $2\mu m$  の注入マスク厚で注入阻止が可能であることが分かる。図 2 は下地層上に  $SiO_2$  膜を堆積し、注入 マスクとして、パターニング後 RIE で加工した断面観察像である。 $SiO_2$  注入マスク厚みは  $2.2\,\mu$  m であり、急峻な側面加工形状が得られている。また、6 インチ基板上での加工面内均一性についても確認した。これらの結果より、 $SiO_2$  注入マスクを用いて 1MeV クラスの高温イオン注入プロセスが可能であることが分かる。当日は活性化アニールを行ってイオン注入層のシート抵抗を検証した結果、また 6 インチ基板上に作製した SiC DMOSFET の電気特性についても報告する。

図1: SiO<sub>2</sub>中のAl 濃度深さ分布

図2: SiO2注入マスクの断面観察

[1] R. Kosugi et al.: in Proc. Int. Symp. Power Semicond. Devices ICs, 2014, p. 346.