## Multifunctional Phosphonic Acid Self-Assembled Monolayer for Metal Patterning and Ultrathin Gate Dielectrics in Fabrication of MoS<sub>2</sub> Field-Effect Transistors QNERC, Institute of Innovative Research, Tokyo Institute of Technology

Wanjing Du, Takamasa Kawanago and Shunri Oda

E-mail: du.w.aa@m.titech.ac.jp

**[Introduction]** This study describes the applications of a self-assembled monolayer (SAM) to the fabrication of  $MoS_2$  FETs. SAM has the ability to generate highly aligned electrodes and provide excellent electrical insulation [1]–[3]. The fabrication process of  $MoS_2$  FETs includes removing metal layer on SAM and the utilization of SAM as an ultrathin gate dielectrics. This methods enables a rapid route to fabricate  $MoS_2$  FETs accompanied by low driving voltage.

[Device Fabrication] 80 nm of aluminum (Al) for gate electrodes was deposited by thermal evaporation on photoresist. Next, aluminum oxides (AlO<sub>x</sub>) and SAM were formed at the surface of Al [3]. The substrate was exposed to oxygen plasma to form  $AlO_x$  and hydroxyl groups on the surface of Al. The substrate was immersed into 2-propanol containing 5 mM n-octadecylphosphonic acid (ODPA) for 1 hour at room temperature. Then, lift-off process was performed to remove the photoresist. 10 nm of Al and 40 nm of gold (Au) entirely. were deposited on the substrate Subsequently, selective removal of Al/Au on ODPA was conducted by sonication in acetone since the ODPA can weakens adhesion strength. The SAM layer was newly formed as gate dielectrics. Finally, mechanically exfoliated MoS<sub>2</sub> flakes were transferred to the substrate with the PDMS elastomer and a mask contact aligner [4].

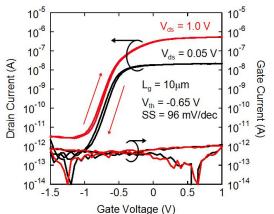

**[Results and Discussions]** The  $I_d-V_g$  characteristics of  $MoS_2$  FET is shown in FIG. 1. Low driving voltage and low gate leakage current were accomplished with SAM-based gate dielectrics owing to ultrathin and close-packed structure of SAM. Threshold voltage ( $V_{th}$ ) of -0.65 V and subthreshold slope (SS) of 96 mV/dec were evaluated from the  $I_d-V_g$  characteristics. Hysteresis in clockwise direction indicates the electron trapping in SAM or  $MoS_2/SAM$  interface [5].

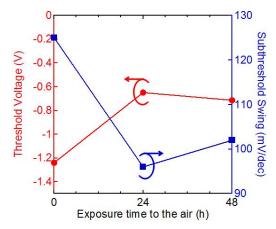

FIG. 2 represents the changes in  $V_{th}$  and SS as a function of exposure time to the air. Time-dependent instability of electrical characteristics was observed from experimental results. This instability is thought to be caused by the absorption of oxygen molecules into sulfur or defect sites on the MoS<sub>2</sub> surface [6].

FIG. 1.  $I_d$ -V<sub>g</sub> characteristics of MoS<sub>2</sub> FETs with SAM-based gate dielectrics.

FIG. 2. Instability of  $V_{th}\xspace$  as a function of exposure time to the air.

**[Conclusions]** This study proposes the simple and rapid process for the fabrication of MoS<sub>2</sub> FETs by exploiting the various functions of SAM. The MoS<sub>2</sub> FETs were successfully operated at low driving voltage with low gate leakage current. This study opens up intriguing features of SAM for building functional electronic devices.

## [References]

- [1] J. C. Love et al., Chem. Rev. 105, 1103 (2005).

- [2] D. J. Beesley et al., Nat. Commun. 5, 3933 (2014).

- [3] H. Klauk et al., Nature, 445, 745 (2007).

- [4] T. Kawanago et al., Appl. Phys. Lett. 108, 041605 (2016).

- [5] D. K. Schroder, Semiconductor Material and Device Characterization (Wiley, New York, 2005).

- [6] Park W, et al. J. Nanotechnology, 2013, 24(9): 095202.