## 原子層堆積 Al<sub>2</sub>O<sub>3</sub> 膜の電気特性に対する熱処理効果

Annealing effect on electric characteristics of atomic-layer-deposition Al<sub>2</sub>O<sub>3</sub> films 早大ナノ・ライフ <sup>1</sup>, 早大理工 <sup>2</sup>, 名大未来研 <sup>3</sup>; <sup>O</sup>平岩 篤 <sup>1,3</sup>, 松村 大輔 <sup>2</sup>, 大久保 智 <sup>2</sup>, 川原田 洋 <sup>1,2</sup> RONL, Waseda Univ. <sup>1</sup>, Fac. Sci. Eng., Waseda Univ. <sup>2</sup>, IMaSS, Nagoya Univ. <sup>3</sup>

°A. Hiraiwa<sup>1,3</sup>, D. Matsumura<sup>2</sup>, S. Okubo<sup>2</sup>, and H. Kawarada<sup>1,2</sup>

- **1. 緒言** Si·SiC を除く半導体基板に形成した MISFET のゲート絶縁膜には原子層堆積 (ALD)  $Al_2O_3$  膜が有望であるが、そのゲート絶縁膜としての検討は熱酸化  $SiO_2$  膜[1]と比べ乏しい。このような中、 $ALD-Al_2O_3$  膜の電気伝導が空間電荷制限電界放出 (space-charge-controlled field emission, SCC-FE) モデルにより定量的に把握できること[2]、半導体基板側界面付近に形成される正電荷・ダイポールの低減等が課題であること[3]を先に報告した。同課題解決に向け、同電気伝導特性と成膜後の熱処理温度との関係について報告する。

- **2. 実験方法**  $2-4\Omega$  cm op 型 (100) CZ-Si 基板を  $77^{\circ}$ C にて APM 洗浄した後、同基板上に TMA と  $H_2$ O を 用いた ALD 法により  $100^{\circ}$ C にて  $Al_2O_3$  膜を 35nm op 厚さに形成した。ついで、 $125-450^{\circ}$ C op  $4%H_2$  (Ar 希釈) 雰囲気中にて 45 分間熱処理 (post-deposition annealing、PDA) した後、抵抗加熱法により Au、Al をマスク蒸着 (開孔寸法  $200\times200$   $\mu$ m) することによりゲート電極を形成し試料を完成させた。なお、ALD を  $100^{\circ}$ C にて行った のは、ブリスタ (半球状の膨れ) が生じにくく、かつ基板側正電荷・ダイポールが比較的少なく正バイアスに対するリーク電流が少ないために、熱処理により負バイアス特性を改善することができれば高温形成膜を凌駕する ゲート絶縁膜を形成することができるものと期待したためである。

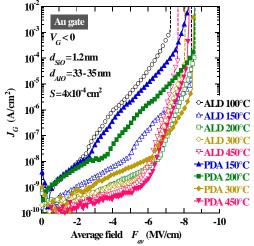

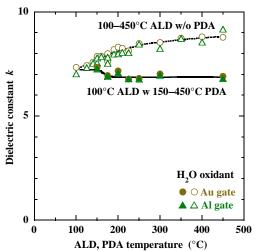

- 3. 結果とその検討 (1)負バイアスに対するリーク電流(図1) 200℃以下の熱処理ではわずかに減少するのみであるが、300℃以上では同一温度にて形成した膜より SCC-FE 成分が少ない。ただし、300℃の場合、trap-assisted tunneling (TAT)起因と思しき低電界成分が残存する。(2)正バイアスに対するリーク電流 熱処理温度がいずれの場合においても、同一温度にて形成した膜より SCC-FE 成分が少ない。しかし、200℃以下の場合、負バイアスに対するのと同様、低電界成分が残存する。(3)熱処理により誘電率が若干減少する(図2)ので上記したように SCC-FE 成分が若干減少しても MISFET 特性の改善にはつながらず、正バイアスのリーク電流を低減する課題が依然として残る。

- **4. 結言**  $H_2O$  による基板の酸化を抑止する必要がある等特殊な場合を除き、熱処理を行うよりも ALD をより高温にて行う方がリーク電流低減には効果的である。いずれにせよ、基板側正電荷・ダイポールの低減が今後の課題である。

【謝辞】 本研究遂行にあたり科研費基盤研究(S)(No.26220903)の助成を得た。

【参考文献】[1] E. H. Nicollian, et al., "MOS (Metal Oxide Semiconductor) Physics and Technology" (Wiley, 1982).

[2] A. Hiraiwa, et al., J. Appl. Phys. 119 (2016) 064505. [3] 平岩、他、第 63 回春応物 20p-S221-4 (2016)、投稿中。

Fig. 1 Leakage currents of ALD-Al<sub>2</sub>O<sub>3</sub> MIS capacitors under negative bias vs average field in gate insulator.

Fig. 2 Dielectric constants of ALD-Al<sub>2</sub>O<sub>3</sub> films vs ALD (open), PDA (filled) temperature.