## 走査型非線形誘電率顕微鏡による SiO<sub>2</sub>/4H-SiC 界面の局所容量特性評価

Evaluation of Local Capacitance Characteristics of SiO<sub>2</sub>/4H-SiC Interface

## by Scanning Nonlinear Dielectric Microscopy 東北大通研 <sup>○</sup>山岸裕史,茅根慎通,長康雄

Res. Inst. of Electrical Commun., Tohoku Univ., OYuji Yamagishi, Norimichi Chinone, Yasuo Cho

E-mail: yamagishi@riec.tohoku.ac.jp

[はじめに] SiC MOS 型電界効果トランジスタの高性能化・高信頼性化のために、SiO<sub>2</sub>/SiC 界面の物性解明と制御は重要である。半導体/酸化膜界面の評価手法として C-V 法や DLTS などの容量測定をベースとした手法が広く用いられているが、我々は試料の局所的な容量特性を測定可能な走査型非線形銹電率顕微鏡 (SNDM) [1] を用いた評価手法を提案している。SNDM は走査プローブ顕微鏡の一種であり、探針直下の容量特性をナノスケールで高感度に測定できる。本研究では、MOS キャパシタ試料への印加バイアスを掃引した時の容量特性の変化を SNDM で試料上の各点で測定し、試料の界面準位密度の評価を行った内容について報告する。

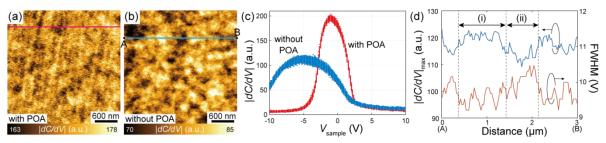

[実験と結果] n型 SiC 基板の Si 面に 20 nm の熱酸化膜が形成された試料を評価対象として用いた。NO 雰囲気下で POA 処理された試料と POA 処理のされていない試料の二種類の試料に対して SNDM 測定を行った。まず変調信号の周波数を 1 MHz、試料に印加するバイアス電圧は 0 V として|dC/dV|像を取得した。この時取得された|dC/dV|像を図1(a)と図1(b)にそれぞれ示す。走査領域の面内では|dC/dV|が空間的に不均一に分布しており、特に POA 処理されていない試料では面内での容量特性のばらつきが大きいことが分かる。次に図1(a)内の赤線と図1(b)内の青線で示した線上で測定された、|dC/dV|と半導体層への印加バイアスの関係を図1(c)に示す。|dC/dV|のピークが確認できるが、このうち POA 処理されていない試料ではピークの最大値(|dC/dV|max) が相対的に小さく、またピークの半値全幅(FWHM)は大きい。これは POA 処理されていない試料の界面準位密度が相対的に高く、金属探針/酸化膜/半導体で構成される MOS 構造の C-V 特性が"stretch-out"していることに対応すると考えられる。さらに図1(b)の線分 AB 上における|dC/dV|max と FWHM の分布を図1(d)に示す。相対的にはC/dV|max が大きく FWHM が小さい領域i)と、その逆の傾向を示す領域ii)が存在していることが確認できるが、これらの領域はそれぞれ界面準位密度が低い領域と高い領域に対応していると考えられ、界面準位密度が面内で不均一に分布していることが示唆される。

**| 謝辞**| 本研究は SIP (戦略的イノベーション創造プログラム)/次世代パワーエレクトロクスによって実施された。 | **参考文献** [1] Y. Cho, A. Kirihara, T. Saeki, Rev. Sci. Instrum. **67** (1996) 2297

図 1 (a) POA 処理された試料と(b) POA 処理のされていない試料の|dC/dV|像. (c) 各試料での|dC/dV|と半導体層への印ルイアスの関係の比較. (d) (b)内の線分 AB 上における $|dC/dV|_{max}$ と FWHM の分布.