## SiO<sub>2</sub>/SiC 界面欠陥由来による局所 DLTS 像の直流バイアス依存性観測

Observation of DC-bias-dependency of local DLTS image related to SiO<sub>2</sub>/SiC interface defects

東北大<sup>1</sup>, 産総研<sup>2</sup>,  $\bigcirc$ 茅根 慎通<sup>1</sup>, 小杉 亮治<sup>2</sup>, 田中 保宣<sup>2</sup>, 原田 信介<sup>2</sup>, 奥村 元<sup>2</sup>, 長 康雄<sup>1</sup>

Tohoku Univ.<sup>1</sup>, AIST<sup>2</sup>, °Norimichi Chinone<sup>1</sup>, Ryoji Kosugi<sup>2</sup>, Yasunori Tanaka<sup>2</sup>, Shinsuke Harada<sup>2</sup>, Hajime Okumura<sup>2</sup>, Yasuo Cho<sup>1</sup> E-mail: chinone@riec.tohoku.ac.jp

<u>はじめに</u> SiC-MOSFET は高効率な電力変換のキーデバイスとして期待されている. しかし特性には改善の余地が大きく, SiO<sub>2</sub>/SiC 界面の欠陥密度低減が重要な課題と言われている. 一般的に行われる平行平板 MOS キャパシタによる SiO<sub>2</sub>/SiC 界面欠陥計測は定量的かつ高感度という優れた特徴を有しているが, 得られる情報は広い領域の平均である. 界面欠陥の性質や起源についてより深く理解するには顕微的な測定による分析が必要になると考えられる. 著者らは前回の応用物理学会春季学術講演会で超高次走査型非線形誘電率顕微鏡法(超高次 SNDM) を応用した探針により欠陥を検出する局所 DLTS 法を提案した[1]. 本報告では提案手法で界面欠陥由来の情報が得られていることを検証するために局所 DLTS 像の DC バイアス依存性を調査した.

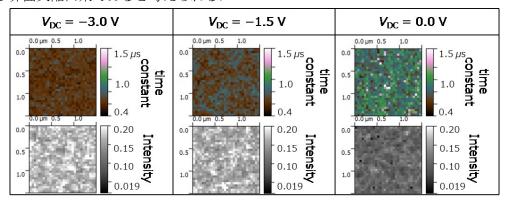

実験および結果と考察 熱酸化により Si 面に 45 nm の酸化膜を形成させた n 型 4H-SiC 基板を用意した. 試料表面に半径 150 nm の金属コート探針を接触させてスキャンし局所 DLTS 測定を行った. 印加したサンプルバイアスは,振幅 1.5 V,周波数 100 kHz,デューティ比 5%の繰り返しパルス電圧である. その際,パルス電圧に-3.0 V,-1.5 V,0.0 V の直流バイアス  $V_{DC}$  を重畳させた. Fig. 1 に各  $V_{DC}$  において得られた局所 DLTS 像(過渡応答の時定数及びスペクトラムの強度の 2 次元像)を示した.  $V_{DC}$  を-3.0 V から 0 V まで変化させると時定数は長く,DLTS 信号の強度は低くなったことが分かる. サンプルの  $V_{DC}$  を負にすることは界面に於けるフェルミレベルを伝導帯に近づけることに対応する. 従ってより伝導帯に近い欠陥が観測されるため過渡応答の時定数は短くなる. また本試料の界面欠陥は伝導帯に近づくほど高密度になることが分かっているため  $V_{DC}$  を負にすると局所 DLTS 信号強度は強くなると考えられる. 以上のように,予想される界面欠陥の応答の VDC 依存性は実験結果と矛盾しない. 以上の考察から本手法で得られている結果はSiO<sub>2</sub>/SiC 界面欠陥由来であると考えられる.

Fig. 1: Images of time-constant and local DLTS intensity obtained at different DC bias are shown. The time-constant gets longer with increasing the DC bias from negative value to zero. In contrast, local DLTS intensity gets smaller with increase of DC bias.

<u>謝辞</u> 本研究の一部は、SIP/次世代パワーエレクトロニクス及び科学研究費補助金基盤研究 S(23226008)、日本学術振興会特別研究員制度の補助を受けている.

参考文献 [1]茅根慎通ら:第 63 回応用物理学会春季学術講演会 20p-H101-9 (2016)