## SiC-MOSFET における伝導帯近傍のドナー型トラップが電気特性に与える 影響のシミュレーション解析

Simulation analysis of an effect on electrical charactaristics of SiC-MOSFET by

donor-type trap near conduction band edge

大阪大学大学院工学研究科

°桶田修平. 西村正. 鎌倉良成

Osaka Univ., °Shuhei Oketa, Tadashi Nishimura, Yoshinari Kamakura

E-mail: oketa@si.eei.eng.osaka-u.ac.jp

[目的] SiC-MOSFET の一層の展開に向け、プロセス・デバイスシミュレータとモデル高精度化が重要である。SiO₂/SiC 界面近傍のアクセプタ型トラップによる可動キャリア減少とクーロン散乱の影響評価によって移動度モデル高精度化研究が進められている。一方、ドナー型トラップの帯電⇔中性化の動きも界面ポテンシャル変化には影響が大きい。最近、伝導帯端近傍にドナー型トラップが存在することが報告されたが[1,2]、我々はそれら二種類のトラップに加え、従来から知られている価電子帯近傍のドナー型トラップをも含めてモデル化を検討している。

今回は製品 SiC-MOSFET の C-V 特性実測結果をシミュレーション解析することで、それぞれのトラップ、とりわけ伝導帯側ドナー型トラップが SiC-MOSFET の電気特性に与える影響を調べた。

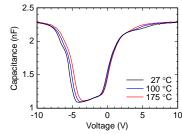

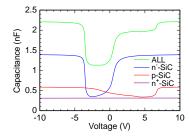

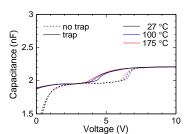

[方法・結果] Fig. 1 は市販の SiC-nMOSFET (耐圧 1,200 V)を、温度を変えて C-V 測定(100 kHz)した結果である。また、Fig. 2 は、報告された構造図[3]をもとに C-V 特性のシミュレーションを行った結果である。但し、いずれのトラップも絶縁膜中の固定電荷も導入していない。実測結果は並置されたソース付 pMOS、nMOS キャパシタの C-V 合成波形であることが分かる。トラップを導入したシミュレーション波形を含め、実測との比較・解析から波形の各変化領域における傾き、肩の出現などとドナートラップの関与を推定できた。温度特性については真性キャリア密度の温度変化の寄与が大きいことを確認した。Fig. 3 は、報告された界面状態密度[4]をもとに伝導帯側ドナー型トラップを導入した nMOSFET の反転側(閾値)シミュレーション結果である。閾値低下と C-V 特性の傾き(界面ポテンシャル変化割合)鈍化に、温度変化よりもドナー型トラップの存在の影響が大きいことを示している。

[1] V. Uhnevionak, Simulation and Modeling of Silicon Carbide Devices, Friedrich-Alexander-Universität, 2015, Ph.D. thesis. [2] H. Yoshioka et al., J. Appl. Phys. 112, 024520 (2012). [3] Fu et al., IEEE Trans. Indust. Appl. 48, 182 (2012). [4] S. Nakazawa et al., IEEE Trans. Electron Devices, 62, 309 (2015).

**Fig. 1:** Measured results of *C-V* characteristics.

**Fig. 2:** Simulation results of *C-V* characteristics of each part of SiC-MOSFET.

**Fig. 3:** Simulation results of *C-V* characteristics with (solid line) and without (dashed line) donor-type trap.