# REALD 形成 Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/p-Ge MOS キャパシターの電気的特性に及ぼす ゲート電極金属の影響

Effects of gate-electrode metals on the electrical properties of Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/p-Ge MOS capacitor grown by REALD

諏訪東京理科大学<sup>1</sup>,山梨大学<sup>2</sup>,弘前大学<sup>3</sup> <sup>○</sup>山田大地<sup>1</sup>,王谷洋平<sup>1</sup>, 山本千綾<sup>2</sup>,山中淳二<sup>2</sup>,佐藤哲也<sup>2</sup>,岡本浩<sup>3</sup>,福田幸夫<sup>1</sup>

Tokyo Univ. of Science, Suwa, <sup>1</sup> Univ. of Yamanashi, <sup>2</sup> Hirosaki Univ.<sup>3</sup> D. Yamada, Y. Otani, C. Yamamoto, J. Yamanaka, T. Sato, H. Okamoto,<sup>3</sup> and Y. Fukuda<sup>1</sup> E-mail: y-fukuda@rs.suwa.tus.ac.jp

#### 1. はじめに

ゲート絶縁膜形成後に行う PDA (Post-deposition annealing) 処理や MOS キャパシター形成後に行う PMA (Post-metallization annealing) 処理は Ge MOS キャパシ ターの電気的特性改善に有効とされているが、その効果の詳細については不明な点が多い。今回、ゲート電極用金属とし て金属酸化物に対する還元性が強い Al と弱い Pt を用いた  $A1_2O_3$ (3. 2nm) / $GeO_2$ (1. 7nm) /p-Ge MOS キャパシターを作製し、その電気的特性に及ぼす PDA 処理および PMA 処理の効果を詳 しく検討したので報告する。

## 2. 実験方法

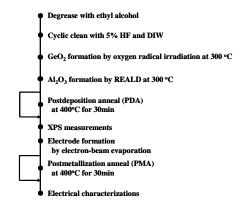

Fig. 1 に試料作製および測定の手順を示す。p-Ge 基板の洗浄後、基板温度 300℃で酸素ラジカル酸化により 1.7nm 厚の GeO₂層を、TMA と酸素ラジカルの交互供給により 3.2nm 厚の A1₂O₃層を形成した。A1 および Pt 電極は UHV チャンバー内で電子ビーム番音により基板が開いた。PA とび TANA #T THE CONTROL OF THE TEST PDA および PMA 処理は 400℃で 30 分間、N<sub>2</sub> + 0-10% H<sub>2</sub>雰囲気

### 3. 結果と考察

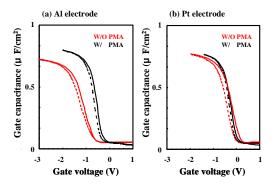

Fig. 2に A1 電極および Pt 電極 MOS キャパシターに対する PMA 処理前後の C-V 特性の変化を示す。(a) より、A1 電極では PMA 処理によるゲート容量( $C_{ox}$ )の増加や界面トラップ密度( $D_{it}$ )の低減、フラットバンド( $V_{fb}$ )の大きな正シフトが見られる。一方、(b) より、Pt 電極の場合は as-deposited の状態で比較的良好な特性が得られており、PMA 処理による特性変化がかない。これらの比較結果上り、A1.0 ( $C_{ox}$ ) ( $C_{ox}$ ) スタ 変化が少ない。これらの比較結果より、Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/p-Ge スタックは ALD 形成時点で良好な電気的特性を有しており、これ 変化が少ない。 が Al 電極蒸着により特性劣化し、さらに PMA 処理により回 復する、と推論できる。 Fig. 3 に、 Al 電極

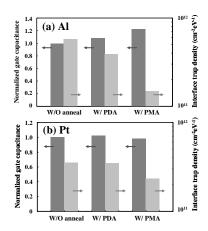

Al 電極および Pt 電極 MOS キャパシターに対 する PDA 処理および PMA 処理が  $C_{\infty}$  および  $D_{i_1}$  に及ぼす効果を示す。なお、 $C_{\infty}$  は熱処理無しの値で規格化して示している。 (b) より、Pt 電極の場合は PDA 処理および PMA 処理による  $C_{\infty}$ の変化が全くないこと、PDA 処理による  $D_{it}$  の変化がまったくないことが分かる。ただし、これらの  $D_{it}$  の値は A1 電極 MOS キャパシターの熱処理無しの値の約半分である。さらに、電 を全属に関係なく、PDA 処理後と PMA 処理後の Dit の比較より、電極素着プロセスにより新たな界面トラップが発生し、これが PMA 処理により低減していることが分かる。界面トラップ発生の原因としては電子ビーム蒸着時に金属ターゲットで発生する X 線や DUV が挙げられる。

A1 電極 MOS ヤイシターで見られた電気的特性劣化の原因としては、サインターで見られた電気的特性劣化の原因としては、サインターで見られた電気的特性劣化の原因としては、サインターである。

Al 电像 MOS イヤハング C元の40に电X時間はカロンが 因としては、先ず、前述の電子ビーム蒸着時に Al ターゲットで発生する放射が考えられる。しかし、Pt の融点は Al よりも高く蒸着時の投入パワーも格段に大きいことから、同様の特性劣化は Pt 電極 MOS キャパシターでも顕著に発生するのち上り、サルカス 全属推議時には貴 と思われる。これらの点より、我々は Al 金属堆積時に非常 に活性な A1 原子が基板  $A1_2O_3$  表面を還元することが原因ではないかと考えている。 **4. まとめ**「一下電極として A1 および Pt を用いた  $A1_2O_3/GeO_2/p-Ge$

MOS キャパシターの電気的特性に及ぼす PDA および PMA 処理 の効果を検討した。その結果、熱処理の効果は電極金属によって異なることが明らかになった。

**謝辞** 本研究は一部科研費の助成のもとに行われた。

Fig. 1. Flow of experiments

Fig. 2. Changes of C-V characteristics of MOS capacitors before and after PMA treatment: (a) Al electrode and (b) Pt electrode.

Fig. 3. Changes of normalized  $C_{\text{ox}}$  and  $D_{\text{it}}$  by PDA and PMA treatments: (a) Al electrode and (b) Pt electrode.