## メタル S/D 型 Ge n-MOSFET の寄生抵抗低減

Decrease in parasitic resistance for metal S/D Ge n-MOSFET

$^{\circ}$ 建山 知輝 $^{1}$ ,永冨 雄太 $^{1}$ ,田中 慎太郎 $^{1}$ ,山本 圭介 $^{2}$ ,王 冬 $^{1}$ ,中島 寬 $^{2}$

## (九大・大学院総合理工学府1,九大・産学連携センター2)

°Tomoki Tateyama <sup>1</sup>, Yuta Nagatomi <sup>1</sup>, Shintaro Tanaka <sup>1</sup>, Keisuke Yamamoto<sup>2</sup>, Dong Wang <sup>1</sup>, Hiroshi Nakashima <sup>2</sup> (I-Eggs, Kyushu Univ. <sup>1</sup>, KASTEC, Kyushu Univ. <sup>2</sup>) E-mail: 2ES15033T@s.kyushu-u.ac.jp

## 1.はじめに

Ge-CMOS の研究開発が加速しているが、n-MOSFET の性能水準は未だ低く、その特性向上は Ge-CMOS を実現する上で重要である。課題の 1 つが Fermi level pinning 現象で、いかなるメタルを用いても Fermi level の位置が価電子帯近傍にピンされる。そのため、低い電子障壁コンタクトの実現は困難とされてきた[1]。これに対し、我々は TiN をスパッタ堆積することで低電子障壁を実現し、更に TiN-S/D 型 n-MOSFET のトランジスタ動作を報告している[2]。しかし、デバイスの EOT が 50 nm と厚いこと、電子移動度が  $220~{\rm cm}^2{\rm Vs}^{-1}$  と低いこと、等の課題がある。EOT を低減すれば、チャネル抵抗が低減して電流駆動力は向上する。しかし、S/D の寄生抵抗( $R_p$ ) が大きい時には  $R_p$  が駆動電流を律速する。今回、S/D の埋込み構造が S/D の低減に有効であるとの知見を得たので報告する。2.試料作製

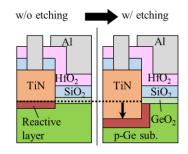

p 形(100) Ge 基板を使用した. 基板の化学洗浄後, S/D 領域のパターニングを行い, 0.03%- $H_2O_2$  を用いて S/D 領域を深さ 12 nm まで掘り込んだ. また, 掘り込み無しの試料も準備した. その後, S/D 領域に 30 nm-TiN を堆積し,  $400^{\circ}$ C-20 min の PMA を行った. 続いてゲート絶縁膜として  $HfO_2/SiO_2/GeO_x$  構造を形成した. その後,  $400^{\circ}$ C-30 min の PDA を行い, ゲート電極として Al を真空蒸着・加工し, 最後にコンタクト電極を形成して TiN-S/D 型 n-MOSFET を作製した. (Fig. 1) チャネル長(L) は 40, 60 および 100  $\mu$ m, チャネル幅(V) は 390  $\mu$ m である. 3.電気特性

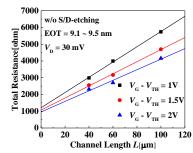

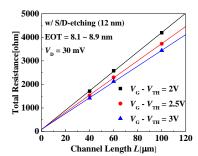

Fig. 2 に掘込み無し n-MOSFET の L と伝達特性より算出したデバイス抵抗との関係を示す. このプロットから算出した  $R_{\rm p}$  は ~1200  $\Omega$  となり,この値は我々グループが既に報告している PtGe-S/D 型 p-MOSFET の  $R_{\rm p}$  ~50  $\Omega$  と比べて非常に大きい[3].  $R_{\rm p}$  が大きい原因として,金属/Ge 界面の反応層の違いが考えられる。Pt/Ge コンタクトの場合,PtGe の反応層は 20 nm と厚く,pn 接合 S/D と同様な埋込み構造が自己整合的に形成される。しかし,TiN/Ge コンタクトの場合,その界面層の厚さは 1~2 nm と極めて薄い[4]. そのため,ソースからの電子の注入効率が低く, $R_{\rm p}$  が高くなっていると考えられる。この問題を解決するため,Fig. 1 に示すように,TiN-S/D を埋込み構造にしてチャネルとの接触面積を増加させた。この掘込み有り n-MOSFET の L とデバイス抵抗との関係を Fig. 3 に示す.埋め込み構造 S/D の場合  $R_{\rm p}$ ~100  $\Omega$  と小さく,約 1 桁の低減に成功した.詳細な特性および掘り下げ深さと  $R_{\rm p}$  との関係については本講演で述べる.

参考文献: [1] A. Dimoulas et al., APL **89**, 252110 (2006). [2] K. Yamamoto et al., APEX **5**, 051301 (2012). [3] Y. Nagatomi et al., JJAP **54**, 070306 (2015). [4] K. Yamamoto et al., APL **104**,132109 (2014).

Fig. 1. Structures of metal S/D n-MOSFET.

Fig. 2. Relation between total resistance and channel length for n-MOSFET without buried S/D structure.

Fig. 3. Relation between total resistance and channel length for n-MOSFET with buried S/D structure.