## Charge retention characteristics of charge trapping nonvolatile memories with silicon carbonitride (SiCN) dielectrics (II)

S. R. A. Ahmed<sup>1</sup>, F. Uehara<sup>2</sup>, and <sup>\*</sup>K. Kobayashi<sup>1,2</sup>

<sup>1</sup> Course of Science and Technology, Graduate School of Science and Technology, Tokai University

<sup>2</sup> Course of Electrical and Electronic System, Graduate School of Engineering, Tokai University

\* Course of Science and Technology, Graduate School of Science and Technology, Tokai University, 4-1-1 Kitakaname, Hiratsuka,

Kanagawa 259-1292, Japan; <u>kkbys@keyaki.cc.u-tokai.ac.jp</u>

**Introduction** The MONOS (Metal-Oxide-Nitride-Oxide-Silicon)-type nonvolatile memory (NVM) have become essential components in the data storage for communication and multimedia applications. However, the MONOS-type memories still face some challenges. Recently, we have proposed the application of silicon carbonitride (SiCN) films to the charge trapping layers.<sup>[1-7]</sup> The relative dielectric constant of the SiCN films is 4.8-4.9, which is lower than that of silicon nitride films (~7). This would result in low power consumption and high programming and erasing speeds in the SiCN-based NVMs. We have previously reported the charge retention characteristics of the SiCN memory capacitors at different temperatures.<sup>[6,7]</sup> The retention life time in the SiCN memory capacitors was estimated to be larger than 10 years at 85 °C. In the present study, we investigated the charge retention behavior of the SiCN memory capacitors and proposed a simple new method to analyze the energy distribution of electron trap states in the forbidden gap of the SiCN layer numerically.

**Experimental procedures** A tunnel oxide film of 2.4 nm in thickness was first formed on p-type (100) silicon substrates by rapid thermal oxidation technique. A 31.5-nm-thick SiCN film was grown at 400 °C using Si(CH<sub>3</sub>)<sub>4</sub> and NH<sub>3</sub> gases by PECVD. A 17.3-nm-thick blocking oxide film was grown using a PECVD technique. Finally, an aluminum film was deposited to form the gate electrode on the oxide-SiCN-oxide stacked films. After the electron injection from the silicon substrate into the SiCN layer, the charge retention characteristics were measured at four different temperatures ranging from room temperature to 235 °C.

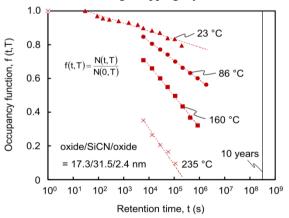

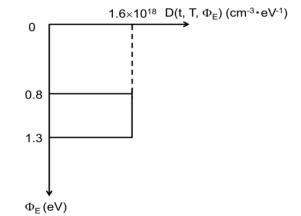

**Results and discussion** We define the occupancy function f(t,T) as the ratio of the density of filled trap states at the retention time t and the testing temperature T to the density of filled trap states at t=0 s. Figure 1 shows the f(t,T) as a function of retention time t for the SiCN memory capacitors in the programming condition at four different temperatures. We can see in Fig. 1 that the electron emission rate df(t,T)/dlog t was larger for the higher testing temperature. The electron emission from the trap sates was thermally activated at the high temperatures. The energy distribution of electron trap states in the SiCN layer for the programming condition was extracted using the proposed simple new method, which needs no adjustable parameters. The electrons trapped in the SiCN layer was found to be distributed from 0.8 to 1.3 eV below the conduction band edge, as shown in Fig. 2. We suggest that the presence of such deep traps resulted in the long-term data retention in the SiCN-based memory capacitors. Hence, the SiCN dielectric films with a low-dielectric constant can be considered as a potential candidate for the charge trapping layer of NVMs.

**Fig. 1.** Occupancy function f(t,T) as a function of retention time t at four different temperatures.

**Fig. 2.** Energy distribution of electron trap states in the SiCN charge trapping layer.

**Acknowledgement** We would like to express gratitude to S. Naito, S. Tanaka, H. Shibayama and J. Nakamura for their valuable discussions. This work was partly supported by JSPS KAKENHI Grant Number 26420280.

**References** [1] S. Naito, S. Nakiri, Y. Ito, H. Shiraiwa, and K. Kobayashi, Ext. Abstr. (The 74th Autumn Meet., 2013); Japan Society of Applied Physics, 18p-P10-9 [in Japanese]. [2] S. Naito, S. Nakiri, and K. Kobayashi, Ext. Abstr. (The 224th Meet., 2013); ECS, 2007. [3] Y. Ito, S. Naito, and K. Kobayashi, Ext. Abstr. (The 61st Spring Meet., 2014); Japan Society of Applied Physics, 18p-PA12-7 [in Japanese]. [4] S. Naito, Y. Ito, and K. Kobayashi, Ext. Abstr. IUMRS-ICEM (2014); 0357. [5] K. Kobayashi, S. Naito, S. Tanaka, and Y. Ito: ECS Trans. 64 (2014) 85. [6] S. R. A. Ahmed, S. Naito, H. Shibayama, J. Nakamura, and K. Kobayashi, Ext. Abstr. (The 62nd Spring Meet., 2015); Japan Society of Applied Physics, 12a-P12-3 [in English]. [7] S. R. A. Ahmed, S. Naito, and K. Kobayashi, ECS Trans. 69 (2015) 99.