# Ar プラズマエッチングを用いた二段階ゲートリセス構造を持つ InGaAs 系 HEMT の試作とその特性

InGaAs-HEMTs with two-step recessed gates by Ar plasma etching 東北大通研,○細谷 友崇、尾辻 泰一、末光 哲也

RIEC, Tohoku Univ., °T. Hosotani, T. Otsuji, T. Suemitsu

## E-mail: tomo@riec.tohoku.ac.jp

### 1, はじめに

InGaAs 系 HEMT はミリ波・サブミリ波帯でのキーデバイスとして注目されている。素子のバラッキを抑えるため、ゲート電極とチャネル部分の間に InP エッチストップ層を挿入したエピ構造が幅広く用いられている。しかし、この InP エッチストップ層はゲート電極とチャネル層の距離を広げてしまい、HEMT の高性能化という面からは望ましくない。

本研究では、Ar プラズマによる異方性エッチングを用いて InP エッチストップ層を選択エッチングしたうえでゲート電極を蒸着する、というプロセス[1]を用いて HEMT を試作した。以下にデバイスの測定結果及び考察を報告する。

#### 2、デバイス構造・測定結果

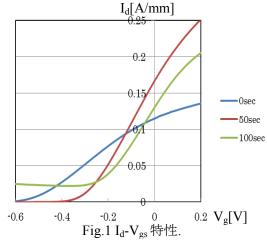

試作には InP 基板上に MOVPE 法によって成長した InAlAs/InGaAs HEMT エピタキシャル結晶を用いた。HEMT 層構造は、表面から n-InGaAs/InAlAs キャップ層 30nm、InP エッチストップ層 6nm、InAlAs バリア層 5nm、 n-InAlAs キャリヤ供給層 5nm、 InAlAs スペーサ層 3nm、 InGaAs チャネル層 15nm、 InAlAs バッファ層 100nm であった。 InP エッチストップ層のエッチングには SAMCO 社製 RIE-10NR を用い、Ar ガス流量 40sccm、Ar ガス圧力 2Pa、RF 出力 50W の条件で行った。 Ar エッチング時間ごとに試作したゲート長 200nm、ゲート幅 100um のデバイスの  $I_d$ - $V_{gs}$  特性を Fig.1 に示す。 Ar エッチングにより関値が正方向に変化した。 Ar エッチングを適用した素子の関値は、InP エッチストップ層を省いたゲート-チャネル間距離で計算した関値とほぼ一致しており、二段階リセス構造が実現できていると推測される。また、最大相互コンダクタンス $(g_m)$ 及び遮断周波数  $(f_T)$ は Ar エッチングを 50 秒行ったもので最大となり、エッチング時間を 100 秒に増やした素子では、 $g_m$ 及び  $f_T$ の低下とオフ電流の増加が観測された。

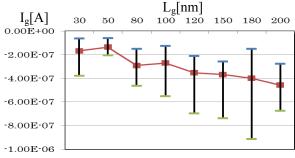

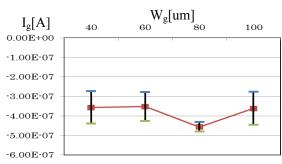

Ar エッチング時間 50 秒のデバイスに注目し、各デバイススペックでゲート電流( $I_g$ )を比較したものを Fig.2-3 に示す。同じゲート幅( $W_g$ )ではゲート長( $L_g$ )が長いほど  $I_g$  は増えたが、同じゲート長では、ゲート幅による  $I_g$  の依存は見られなかった。

#### 3、考察

Ar エッチングによる HEMT の性能向上を確認できた。しかし今回のエッチング条件ではオーバーエッチングによる  $g_m$  の劣化とリーク電流の増加が発生し、選択エッチングの機能を果たすには不十分であった。また、 $I_g$  はゲート幅に依存しないところでリークしていることがわかった。このことより、メサ端などゲート長によらない箇所に  $I_g$  が集中していると思われる。今後は Ar プラズマエッチングについてより低ダメージとなる条件を検討し、閾値の均一性・再現性を確保可能な選択エッチングを確立し、リーク電流を抑えた InGaAs 系 InGaAs 所 InGaAs InGaS InGaS

#### ○謝辞

本研究は、東北大通研付属ナノ・スピン実験施設で行われた。

[1] T. Suemitsu, et al., IEEE Trans. Electron Devices 49 (2002) 1694.

Fig.2  $V_{ds}$ =0.8V,  $V_{g}$ =-0.1V,  $W_{g}$ =100um  $\circlearrowleft O$   $I_{g}$ .

Fig.3  $V_{ds}$ =0.8V,  $V_{g}$ =-0.1V,  $L_{g}$ =200nm  $\circlearrowleft O$   $I_{g}$ .