## HSTP プロセスでの AQFP セルライブラリの設計

# Implementation of AQFP cell library using HSTP

<sup>○</sup>安藤 拓生、竹内 尚輝、山梨 裕希、吉川 信行(横国大)

°Takumi Ando, Naoki Takeuchi, Yuki Yamanashi, Nobuyuki Yoshikawa (Yokohama Nat. Univ.)

## E-mail: ando-takumi-cz@ynu.jp

現在の計算機の主流である半導体集積回路は、微細化の限界が近づいていて、性能の向上、低消費電力性の向上が難しくなってきている。特にエクサスケールのスパコンを実現するにあたり、現在の CMOS プロセッサでは膨大な電力が必要であることが予想される。そこで我々は、CMOS より高速で、超低消費電力である断熱型磁束量子パラメトロン(Adiabatic Quantum Flux Parametron; AQFP)回路[1]の研究を行っている。

これまで我々は、AQFP 回路による大規模演算システムの実現に向けて、セルライブラリの構築を進めてきた。AQFP セルライブラリは、あらゆる論理セルを 4 つのビルディングブロック (Buffer, NOT, Constant, Branch) の組み合わせで実現することができる。AQFP セルライブラリはSTP2 プロセスにおいて広い動作マージンを実証している[2]。

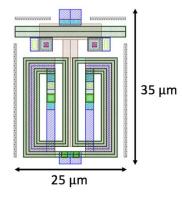

今回我々は新たに HSTP プロセスで AQFP セルライブラリを設計した。 Fig.1 は設計した Buffer セルのレイアウトである。

Table 1 は接合の McCumber パラメータ $\beta_c$ 、最高動作周波数 $f_{max}$ 、エネルギー遅延積(energy-delay product: EDP)をプロセスで比較したもので、Unshunted,Shunted はそれぞれシャント抵抗なし、ありを示している[3]。STP2 プロセスでは、接合に並列にシャント抵抗を接続し、 $\beta_c$ を 1 に調整することで高速動作を可能にしているが、EDP はシャント抵抗なしのときと比べると大幅に増加してしまう。HSTP プロセスでは、シャント抵抗がなくても 12.4GHz の高速動作が可能であり、シ

ャント抵抗ありの STP2 プロセスより EDP が大幅に低いことがわかる。

今回 HSTP プロセスでの AQFP セルライブラ リについて、設計と動作実証を行ったのでそれら について報告する。

Fig. 1. Layout of buffer cell

Table 1. Comparison of fabrication processes[3]

| プロセス           | $eta_c$ | $f_{max}(GHz)$ | EDP(aJ×ps)            |

|----------------|---------|----------------|-----------------------|

| STP2 Unshunted | ~2600   | 1.83           | $4.28 \times 10^{-2}$ |

| HSTP Unshunted | ~190    | 12.4           | $8.57 \times 10^{-2}$ |

| STP2 Shunted   | 1.0     | 47.0           | 2.20                  |

### 謝辞

本研究に使用されたデバイスは、(独)産業技術総合研究所(AIST)の超伝導クリーンルーム CRAVITYにおいて作製された。本研究は JSPS 科研費基盤研究(S)(26220904)の助成を受けたものである。

#### 参考文献

- [1] N. Takeuchi, et al.: Supercond. Sci. Technol., Vol. 26 (2013) p.035010

- [2] N. Takeuchi, et al.: J. Appl. Phys., Vol. 117 (2015) p.173912

- [3] N. Takeuchi, et al.: Supercond. Sci. Technol., Vol. 28 (2015) p.015003