## フラッシュランプアニール(FLA)による高電子濃度かつ高電子移動度の n+poly-Ge 形成 Fabrication of n+poly-Ge Film with High Electron Concentration and High Electron Mobility by Flash-Lamp Annealing (FLA)

<sup>1</sup>(株)東芝 研究開発センター, <sup>2</sup>産総研 連携研究体グリーン・ナノエレクトロニクスセンター, <sup>3</sup>産総研 <sup>1</sup>Corporate R&D Center, Toshiba Corp., <sup>2</sup>Collaborative Research Team GNC, AIST, <sup>3</sup>AIST <sup>○</sup>小池 正浩 <sup>1,2</sup>, 臼田 宏治 <sup>1,2</sup>, 鎌田 善己 <sup>1,2</sup>, 森 貴洋 <sup>2,3</sup>, 前田 辰郎 <sup>2,3</sup>, 手塚 勉 <sup>1,2</sup> M. Koike, <sup>1,2</sup> K. Usuda, <sup>1,2</sup> Y. Kamata, <sup>1,2</sup> T. Mori, <sup>2,3</sup> T. Maeda, <sup>2,3</sup> and T. Tezuka <sup>1,2</sup> m-koike@mail.rdc.toshiba.co.jp

モノリシック 3 次元積層 CMOS を実現する材料として poly-Ge に注目している[1-3]。下層の CMOS 回路に影響を与えない低い温度で poly-Ge は形成できるからである。しかしながら poly-Ge は n型化が難しいという問題があり、poly-Ge からなる MOSFET を作製する場合、n+poly-Ge の形成が困難であることが予想される。Ge では欠陥がアクセプターライクに振る舞う傾向にあり、それに伴う濃度のホールが生成されるため( $\sim 10^{18} \, \mathrm{cm}^{-3}$ )、poly-Ge は通常 p型の特性を示すからである。

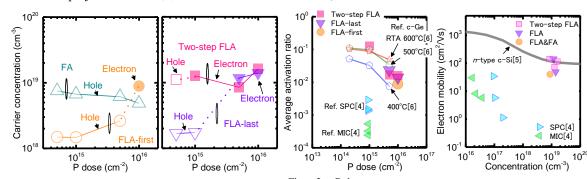

従来までに、二段階フラッシュランプアニール(FLA)により、アモルファス Ge を結晶化してから Pイオン注入し再び結晶化および活性化させると高キャリア濃度かつ高移動度の n+poly-Ge が形成できることを報告した[1]。このように形成した n+poly-Ge からなるトライゲート・ジャンクションレス型 nMOSFETは 119  $\mu$ A/ $\mu$ m という高い駆動電流を示した。

しかしながら、n+poly-Ge 形成するプロセスとして、FLA で結晶化した Ge と結晶化していない Ge(アモルファス Ge)に P イオン注入した場合の違いや、P イオン注入した Ge を FLA とそれ以外の熱処理法で結晶化および活性化した場合の違いは明らかではなかった。そこで本研究では、FLA を含む様々なプロセスで熱処理して n+poly-Ge の形成を試みた。

熱 SiO<sub>2</sub> 膜(~200 nm)/Si(100)基板上に、アモルファス Ge(~100 nm)をスパッター堆積し、その上に PECVD SiO<sub>2</sub> 膜(~5 nm)を堆積して Pイオン注入した( $5 \times 10^{14}$ ,  $1 \times 10^{15}$ ,  $5 \times 10^{15}$ ,  $1 \times 10^{16}$  cm<sup>-2</sup>, 10 keV)。熱 処理プロセスとして本研究では次の 4 つの条件を調べた。(i) Pイオン注入→ファーネスアニール(FA), (ii) FLA→Pイオン注入→ファーネスアニール(FLA-first), (iii) Pイオン注入→FLA (FLA-last), (iv) FLA→Pイオン注入→FLA (Two-step FLA)。FLA は 80 J/cm<sup>2</sup>, 10 ms, FA は  $500^{\circ}$ C,5 h である。こうして形成した poly-Ge に対して以下の分析を行った。構造は断面および平面 TEM 観察、不純物濃度プロファイルは SIMS 分析、結晶方位およびグレインサイズは EBSD、キャリアタイプ、キャリア濃度、移動度(Hall 移動度)は Hall 効果測定により調べた。

電子移動度は電子濃度が $\sim 10^{19}\,\mathrm{cm}^{-3}$ でバルク Si よりも高い  $140\,\mathrm{cm}^2/\mathrm{Vs}$  を示すことがわかった(Fig. 3)。 高電子濃度や高電子移動度は FLA によって poly-Ge のアクセプターライクな欠陥が低減できるためであり、それゆえ欠陥を生じるイオン注入後に FLA した場合に効果的であったと考えられる。

このようにイオン注入後にFLAによって結晶化および活性化熱処理することが高電子濃度かつ高電子移動度の *n*+poly-Ge 形成の本質であることが明らかになった。

Fig. 1: Relationship between carrier concentration and P-dose in poly-Ge fabricated by FA, FLA-first, FLA-last, and two-step FLA. Open symbols indicate holes; closed symbols indicate electrons.

Fig. 2: P-dose vs. average activation ratio. The data for poly-Ge by MIC and SPC [4] and for c-Ge [6] is also depicted.

Fig. 3: Electron mobility of poly-Ge and crystalline Si. The data for the crystalline Si (c-Si) is from [5].

本研究を進めるにあたり、多大なご協力をいただきました産総研テクニカルスタッフの方々に感謝致します。本研究の一部は政府の最先端研究開発支援プログラムにより助成されたものである。

[1] K Usuda et al., IEDM Tech. Dig., 422 (2014). [2] Y. Kamimuta et al., VLSI-TSA, 109 (2013). [3] Y. Kamata et al., SSDM, 668 (2014). [4] H. –W. Jung et al., J. Alloy and Compounds, **561**, 231 (2013). [5] C. Jacoboni et al., Solid State Electron. **20**, 77 (1977). [6] M. Koike et al., J. Appl. Phys. **104**, 023523 (2008).