# Multi-Layer All Sol-Gel Fabrication Technique on Bulk Silicon toward Vertical Coupler

Ahmad Syahrin Idris, Sampad Ghosh\*, Haisong Jiang, and Kiichi Hamamoto

I-Eggs, Kyushu University

E-mail: 2ES15224Y@s.kyushu-u.ac.jp

# I. Introduction

Space division multiplexing (SDM) [1] is a technique that is proposed as one of the main candidate to address the issue of ever increasing demand for greater data transmission. Multi-core fibres (MCF) are a major component in realizing SDM to improve the capacity of data transmission bandwidth [2]. Because an MCF has a 3-dimensional core layout at the fibre facet, issues arise when coupling to MCF from planar photonic circuits such as optical switches, multiplexers, and waveguides. In order to address the coupling issue, a vertical coupled waveguide is an attractive solution [3]. In this work, we propose and fabricate a stacked multi-layer all sol-gel fabrication technique using ZnO and SiO<sub>2</sub> sol-gel on bulk Si to enable the realization of a vertical coupled waveguide.

## **II. Issues in Sol-gel Multilayer Fabrication**

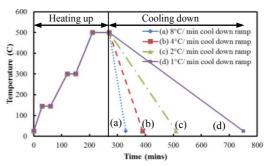

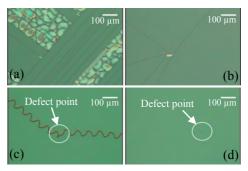

The prepared SiO<sub>2</sub> sol-gel solution was coated onto Si by a spin-coater and then heating was performed by a thermal annealer. Heating and cooling profile is shown in Fig.1. However, deformation (crack) was appeared on SiO<sub>2</sub> sol-gel layer due to stress during the cooling down stages. No crack was looked during the heating up stage because SiO<sub>2</sub> layer is still not fully cured yet. As a result, no stress on SiO<sub>2</sub> layer up to the maximum heating up temperature. Cracks were only observed (Fig.2) when cooling the sample from the maximum annealing temperature down to room temperature. During the cooling down stage, thermal stress that was generated and accumulated in SiO<sub>2</sub> layer is released and due to the thermal coefficient difference between SiO<sub>2</sub> and Si gives rise to the formation of cracks. Fig. 2(a) shows multiple oriented cracks and delamination of the SiO<sub>2</sub> sol-gel layer when cooling down at a rate of 8°C/min that appears over the whole sample. Slowing the cooling rate down to 4°C/min in Fig. 2(b) produces lesser cracks which still occurs over the whole sample but no delamination was observed. In Fig. 2(c), a rate of 2°C/min results only zig-zag cracks that originate from point defects on SiO<sub>2</sub> surface and is significantly less than the previous two cases. Finally, Fig. 2(d) with a rate of 1°C/min gives no cracks on the surface even ones originated from point defects.

### **III. Results and Discussion**

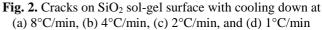

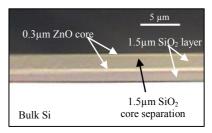

The formation of cracks however can be reduced by controlling the cooling down ramp of the  $SiO_2$  layer. The fabricated device is shown in Fig.3 with the thickness of each layers. Thermal annealing was done in order to

Fig. 3. Stacked multiple layers on bulk Si

densify all the sol-gel layers. All of the thickness were measured after the high temperature annealing process was effectively completed.

#### **IV. Conclusion**

We have successfully stacked multiple layers by all solgel based fabrication technique. The capability to stack ZnO core layer and SiO<sub>2</sub> core separation layers on bulk Si with accurate thickness control enables the realization of vertical coupling.

### **References:**

- [1] T. Moriaka, proc. of OECC 2009, FT4 (2009).

- [2] D. J. Richardson et al., Nat. Photonics, 7 (2013).

- [3] Y. Kokubun et al., IEEE J. Sel. Top. Quantum Electron, 11 (2005).