## トレンチ MOS 構造を設けた Ga<sub>2</sub>O<sub>3</sub> ショットキーバリアダイオード

Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diode with Trench MOS Structure

ノベルクリスタルテクノロジー1, タムラ製作所2, 情通機構3

<sup>○</sup>佐々木 公平<sup>1,2</sup>, 脇本 大樹<sup>1,2</sup>, ティユ クァン トゥ<sup>1</sup>, 小石川 結樹<sup>1,2</sup>, 倉又 朗人<sup>1,2</sup>, 東脇 正高<sup>3</sup>, 山腰 茂伸<sup>1,2</sup>

Novel Crystal Tech.<sup>1</sup>, Tamura Corp.<sup>2</sup>, NICT<sup>3</sup>

\*Kohei Sasaki<sup>1, 2</sup>, Daiki Wakimoto<sup>1, 2</sup>, Quang Tu Thieu<sup>1</sup>, Yuki Koishikawa<sup>1, 2</sup>,

Akito Kuramata<sup>1, 2</sup>, Masataka Higashiwaki<sup>3</sup> and Shigenobu Yamakoshi<sup>1, 2</sup>

E-mail: sasaki@novelcrystal.co.jp

$\beta$ - $Ga_2O_3$  は、材料物性および量産性の点から、次世代の低損失高耐圧パワーデバイス用材料として魅力的である。これまでに  $Ga_2O_3$  SBD の試作を行い、熱電子電界放出(TFE)理論で予測される限界特性に迫る性能を実証した[ $\dagger$ ]。 TFE によるリーク電流を下げるためには、p 型埋め込み構造やトレンチ MOS 構造等をアノード電極直下に形成し、ショットキー接合部の電界強度を低減する手法が有効である。今回、トレンチ MOS 構造を設けた  $Ga_2O_3$  SBD を試作したのでその特性について報告する。

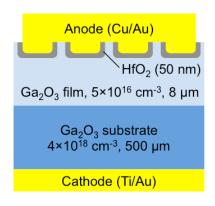

図 1 に試作したデバイスの構造断面模式図を示す。Sn ドープ(001)基板上に、HVPE 法で Si ドープ  $Ga_2O_3$  膜を成長させた。基板およびエピ膜のドナー濃度と厚さはそれぞれ  $4\times10^{18}$  cm<sup>-3</sup>、500  $\mu$ m と  $5\times10^{16}$  cm<sup>-3</sup>、8  $\mu$ m である。エピ膜の表面に、ドライエッチングによりメサ(幅 1  $\mu$ m)とトレンチ(幅 5  $\mu$ m、深さ 2  $\mu$ m)の周期構造を形成した。トレンチ側面及び底面には厚さ 50 nm の  $HfO_2$  膜を設けた。アノード電極として、直径 400  $\mu$ m の Cu/Au を形成した。カソード電極には Ti/Au を用いた。比較のために、同じエピ基板上にトレンチ構造を設けていない通常の SBD も作製した。

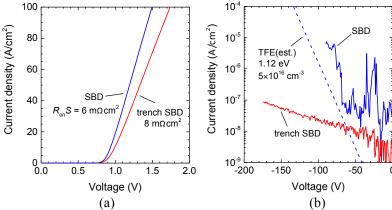

図 2(a)に順方向電流密度-電圧(J-V)特性を示す。トレンチ SBD の方が通常の SBD よりもオン抵抗が高いのは、トレンチの導入により電流経路が減少したためである。図 2(b)に逆方向特性を示す。通常の SBD のリーク特性が TFE 理論にほぼ従うのに対して、トレンチ SBD は通常の SBD より数桁低いリーク特性を示している。 $Ga_2O_3$  SBD においても、トレンチ MOS 構造を導入することによって、逆方向リーク電流の抑制が可能なことを実証できた。

本研究の一部は、総合科学技術・イノベーション会議の SIP(戦略的イノベーション創造プログラム)「次世代パワーエレクトロニクス」(管理法人: NEDO)と文部科学省ナノテクノロジープラットフォーム事業 (NIMS 微細加工プラットフォーム、東京工業大学、早稲田大学)の支援を受けて実施した。

[†]佐々木他、2015年 第76回応物秋期学術講演会16p-4C-8。

Fig. 1 Schematic illustration of  $Ga_2O_3$  trench SBD.

Fig. 2 (a) Forward and (b) reverse *J-V* characteristics.