## Enhancement-Mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs with Si-Ion-Implanted Source and Drain National Institute of Information and Communications Technology<sup>1</sup>, Tamura Corporation<sup>2</sup> <sup>°</sup>Man Hoi Wong<sup>1</sup>, Yoshiaki Nakata<sup>1</sup>, Akito Kuramata<sup>2</sup>, Shigenobu Yamakoshi<sup>2</sup>, Masataka Higashiwaki<sup>1</sup> E-mail: mhwong@nict.go.jp

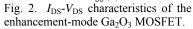

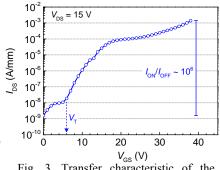

Power converters favor normally-off switches for safety and simplified circuit topologies. Enhancementmode Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors (MOSFETs) reported to date employ relatively high channel doping intended for maintaining volume current density, which imposes constraints on the device dimensions or architecture to realize positive threshold voltage ( $V_T$ ) while limiting conductance in the ungated access regions [1,2]. This work demonstrates enhancement-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs with an unintentionallydoped (UID) Ga<sub>2</sub>O<sub>3</sub> channel, whose low background carrier density ( $n_{UID}$ ) offers improved design flexibility and reduced process complexity for achieving full channel depletion at a gate bias ( $V_{GS}$ ) of 0 V. Low source/drain series resistances were realized by Si-ion (Si<sup>+</sup>) implantation. MOSFETs with a channel length of 4 µm delivered a maximum drain current density ( $I_{DS}$ ) of 1.4 mA/mm and an  $I_{DS}$  on/off ratio ( $I_{ON}/I_{OFF}$ ) near 10<sup>6</sup>.

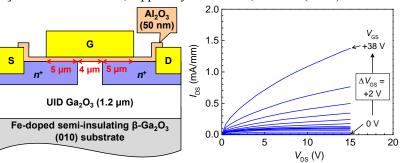

The enhancement-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs consisted of a 1.2-µm-thick UID Ga<sub>2</sub>O<sub>3</sub> epilayer grown on an Fe-doped semi-insulating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrate by ozone molecular beam epitaxy (Fig. 1). Si<sup>+</sup> implantation defined the  $n^+$  source/drain ohmic and access regions. A 50-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric was formed on the Ga<sub>2</sub>O<sub>3</sub> by plasma atomic layer deposition. A gate- $n^+$  overlap of 5 µm at both the source and drain sides led to highly conductive access regions and ensured charge modulation over the entire 4-µm-long channel. MOS capacitors (MOSCAPs) with a 200-µm-diameter circular anode were used for capacitance-voltage (*C-V*) characterization of the Al<sub>2</sub>O<sub>3</sub> dielectric. Vertical Pt/Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes (SBDs) with a 2-µm-thick UID Ga<sub>2</sub>O<sub>3</sub> drift layer were fabricated on a Sn-doped  $n^+$  β-Ga<sub>2</sub>O<sub>3</sub> (010) substrate for extracting  $n_{\rm UID}$ .

*C-V* measurements performed on the SBDs indicated that the UID Ga<sub>2</sub>O<sub>3</sub> drift layer was fully depleted by the built-in voltage, based on which the  $n_{\text{UID}}$  was estimated to be less than  $4 \times 10^{14}$  cm<sup>-3</sup>. The MOSFETs featured small parasitic source/drain resistances, where a sheet resistance of 84  $\Omega$ /sq for the  $n^+$  implant and a metal/semiconductor contact resistance of 0.25  $\Omega$ ·mm yielded a total parasitic resistance of 1.4  $\Omega$ ·mm between source and drain. Despite a low  $n_{\text{UID}}$ , the maximum on-state  $I_{\text{DS}}$  of 1.4 mA/mm was an order of magnitude higher than those reported in Refs. 1 and 2 (Fig. 2). An  $I_{\text{ON}}(V_{\text{GS}}=+38 \text{ V})/I_{\text{OFF}}(V_{\text{GS}}=0 \text{ V})$  ratio of  $9 \times 10^5$  was achieved at  $V_{\text{DS}}=15$  V (Fig. 3). Improved device characteristics can be expected by optimizing the Al<sub>2</sub>O<sub>3</sub> dielectric to eliminate hysteresis, Fermi level pinning, and large  $V_{\text{T}}$  shift that were attributable to a high density of electron traps as revealed by the MOSCAPs.

This work was partially supported by Council for Science, Technology and Innovation (CSTI), Crossministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (funding agency: NEDO).

[1] K. Zeng et al., Proc. 74th IEEE Device Research Conf., pp. 105-106 (2016).

[2] K. D. Chabak et al., Appl. Phys. Lett. 109, 213501 (2016).

Fig. 1. Schematic cross section of the enhancement-mode  $Ga_2O_3$  MOSFET.

Fig. 3. Transfer characteristic of the same MOSFET as extracted from Fig. 2.