## リモートプラズマ支援 CVD SiO<sub>2</sub>/GaN の界面特性

Interface properties of SiO<sub>2</sub>/GaN formed by Remote-plasma-assisted CVD 名大院工<sup>1</sup>, 産総研 GaN-OIL<sup>2</sup> <sup>O</sup>グェンスァン チュン<sup>1,2</sup> 田岡 紀之<sup>2</sup>, 大田 晃生<sup>1</sup>, 山本 泰史<sup>1,2</sup>, 山田 永<sup>2</sup>, 高橋 言緒<sup>2</sup>, 池田 弥央<sup>1</sup>, 牧原 克典<sup>1</sup>, 清水 三聡<sup>2</sup>, 宮崎 誠一<sup>1</sup> Nagoya Univ.<sup>1</sup>, AIST GaN-OIL<sup>2</sup> <sup>O</sup>N. X. Truyen<sup>1,2</sup>, N. Taoka<sup>2</sup>, A. Ohta<sup>1</sup>, T. Yamamoto<sup>1,2</sup>, H. Yamada<sup>2</sup>, T. Takahashi<sup>2</sup>, M. Ikeda<sup>1</sup>, K. Makihara<sup>1</sup>, M. Shimizu<sup>2</sup> and S. Miyazaki<sup>1</sup> E-mail: n\_xua@nuee.nagoya-u.ac.jp

序>SiO<sub>2</sub>は、バンドギャップが~8.9eV と大きく、絶縁破壊強度(>8MV/cm)が高いことから GaN パワーデバイスにおいてもゲート絶縁膜として有望な材料である。しかしながら、GaN 上への SiO<sub>2</sub> の形成は CVD などの堆積によって形成する必要がある[1, 2]。また、SiO<sub>2</sub>/GaN 界面構造の設計指針(どの様な堆積プロセス、界面構造が GaN MOS にとって適切であるか)は良くわかっていない。そこで本研究ではリモートプラズマ支援 CVD により SiO<sub>2</sub>/GaN 界面を形成し、化学的な構造を調べるとともに MOS キャパシタを作製し、SiO<sub>2</sub>/GaN 界面の電気特性を調べた。

実験>エピタキシャル成長した n 型 GaN (0001)表面(不純物濃度 3.0x $10^{16}$ /cm³、膜厚:~2μm)を  $H_2O:H_2O_2:NH_4OH=7:3:0.15$  の混合液により洗浄した後、4.5%の希釈 HF 溶液に浸漬した。その後、  $SiH_4$  と Ar 希釈  $O_2$ (Ar: $O_2=30:20$ )を用いたリモートプラズマ支援 CVD により約~6nm の  $SiO_2$  薄膜を 堆積した。プラズマは石英管に配置したワンターンコイル状アンテナに 60MHz 高周波電力を供給し、誘導結合により励起・生成した。 $SiH_4$ 流量、基板温度、基板-アンテナ間距離および高周波電力はそれぞれ、0.38sccm、500°C、19cm、10W で一定とした。比較として Si 基板上においても同条件において  $SiO_2$  膜を堆積した。一部の試料においては、Al ゲート電極および裏面電極を形成し、MOS キャパシタを作製した。

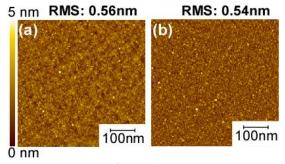

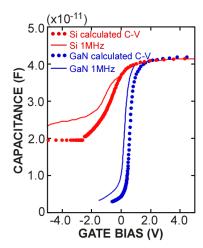

**結果**>Fig. 1 に Si(111)表面及び GaN(0001)表面上に同時に 6nm の SiO $_2$  膜を堆積した場合の表面形状像を示す。基板の違いによる顕著な差は観測されず、表面ラフネスが RMS~0.5nm と比較的平坦な SiO $_2$  膜が形成されており、ゲート絶縁膜として、機能すると考えられる。別途行った XPS 分析では、O1s スペクトルにおいて、Si 基板上の SiO $_2$  に比べて、GaN 基板の場合では低結合エネルギー側に僅かにテールが検出された。このテールは、 $SiO_2/GaN$  界面に僅かに酸素を介した Ga-O-Si 結合に相当する可能性が高い。Fig. 2 に Si 及び GaN MOS キャパシタの 1MHz での容量-電圧(C-V) 特性の結果を示す。比較としてそれぞれの場合における理想 C-V 曲線の計算結果も示す。Si の場合では実測した C-V 曲線は理想 C-V 曲線と大きく異なり、-1V 付近にハンプが見られる。 $CVD-SiO_2/Si$  界面は、一般的に熱酸化  $SiO_2/Si$  と比較して、良い界面形成が困難であることから、本研究においても、同様な結果が得られた可能性がある。一方で、GaN の MOS キャパシタではフラッドバンド電圧から約 0.3V と僅かにずれるものの、理想 C-V 曲線とよく類似した C-V 曲線

が得られた。当日は化学結合状態および電気的特性の詳細について講演を行う予定である。

文献>[1] T. Hashizume et al., J. Vac. Sci. Technol. B **21** (2003) 1828.

[2] J. P. Ao et al., phys. stat. sol. c, 8 (2011) 457.

謝辞>本研究の一部は、NEDO の委託により実施された。

Fig. 1 AFM images of (a) Si(111) and (b) GaN(0001) surfaces taken after deposition of CVD-SiO<sub>2</sub>.

Fig. 2 C-V curves of SiO<sub>2</sub>/Si and SiO<sub>2</sub>/GaN MOS capacitors measured at 1MHz. Ideal C-V curves of them were also shown as references.